### PDP-11/24 System Technical Manual

# PDP-11/24 System Technical Manual

Prepared by Educational Services of Digital Equipment Corporation

1st Edition, June 1981 2nd Edition, February 1984 3rd Edition, January 1985

#### © Digital Equipment Corporation 1981, 1984, 1985 All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

#### Printed in U.S.A.

This document was set on a DIGITAL DECset Integrated Publishing System.

The following are trademarks of Digital Equipment Corporation:

DEC DECmate DECset DECsystem-10 DECSYSTEM-20

DECUS

DECwriter

DIBOL

MASSBUS

PDP

P/OS

Professional

Rainbow

RSTS RSX UNIBUS VAX VMS VT

Work Processor

### **CONTENTS**

Page

| PREFACE   | •                                    |                                         |

|-----------|--------------------------------------|-----------------------------------------|

| CHAPTER 1 | INTRODUCTION                         |                                         |

| 1.1       | MANUAL SCOPE                         |                                         |

| 1.1.1     | DIGITAL Personnel Ordering           |                                         |

| 1.1.2     | Customer Ordering Information        |                                         |

| 1.2       | SYSTEM OVERVIEW                      |                                         |

| 1.3       | PDP-11/24 CENTRAL PROCESSING UNIT    |                                         |

| 1.3.1     | CPU Data and Control Chips           |                                         |

| 1.3.2     | Memory Management                    |                                         |

| 1.3.3     | Operator's Console                   |                                         |

| 1.3.4     | Serial Line Units                    |                                         |

| 1.3.5     | Line Time Clock                      |                                         |

| 1.3.6     | Bootstrap                            |                                         |

| 1.3.7     | UNIBUS Termination                   |                                         |

| 1.3.8     | MS11-L MOS Memory System             |                                         |

| 1.3.9     | MS11-P MOS Memory System             |                                         |

| 1.3.10    | Floating-Point Processor             |                                         |

|           | Commercial Instruction Set Processor |                                         |

| 1.3.11    | GENERAL-PURPOSE REGISTERS            |                                         |

| 1.4       | ADDRESSING MEMORY AND PERIPHERALS    |                                         |

| 1.5       | ADDRESSING MODES                     |                                         |

| 1.6       | INSTRUCTION SET                      |                                         |

| 1.7       | CONFIGURATION                        | •••••                                   |

| 1.8       | CONFIGURATION                        |                                         |

| 1.8.1     | BA11-L Mounting Box                  |                                         |

| 1.8.2     | BA11-A Mounting Box                  |                                         |

| 1.8.3     | System Configuration                 |                                         |

| 1.9       | PDP-11/24 BACKPLANE                  |                                         |

| 1.10      | SPECIFICATIONS                       | ••••••                                  |

| CHAPTER 2 | INSTALLATION                         |                                         |

| 2.1       | GENERAL                              |                                         |

| 2.2       | SITE CONSIDERATIONS                  |                                         |

| 2.2.1     | Humidity and Temperature             |                                         |

| 2.2.2     | Air-Conditioning                     |                                         |

| 2.2.3     | Acoustical Damping                   |                                         |

| 2.2.4     | Lighting                             |                                         |

| 2.2.5     | Special Mounting Conditions          |                                         |

| 2.2.6     | Static Electricity                   |                                         |

| 2.3       | ELECTRICAL REQUIREMENTS              |                                         |

| 2.4       | UNPACKING                            |                                         |

| 2.4.1     | PDP-11/24-AA, -AC, -BC Unit Removal  |                                         |

| 2.4.2     | PDP-11/24 System Cabinet Removal     |                                         |

| 2.5       | INITIAL INSPECTION                   | • • • • • • • • • • • • • • • • • • • • |

| 2.6       | INSTALLATION                         | •••••                                   |

| 2.6.1     | BA11-L Installation                  |                                         |

|           |                                                          | Page |

|-----------|----------------------------------------------------------|------|

|           |                                                          | 2.4  |

| 2.6.2     | BA11-A Installation                                      | 2-9  |

| 2.6.2.1   | Index Plate Mounting                                     |      |

| 2.6.2.2   | Slide Assembly Mounting                                  |      |

| 2.6.2.3   | Mounting Box-to-Slide Installation                       |      |

| 2.6.3     | PDP-11/24 System Cabinet Installation                    |      |

| 2.6.4     | Expander Cabinet Installation                            | 2-20 |

| 2.7       | MODULE UTILIZATION IN A TYPICAL SYSTEM                   |      |

| 2.8       | MODULE JUMPER AND SWITCH CONFIGURATIONS                  |      |

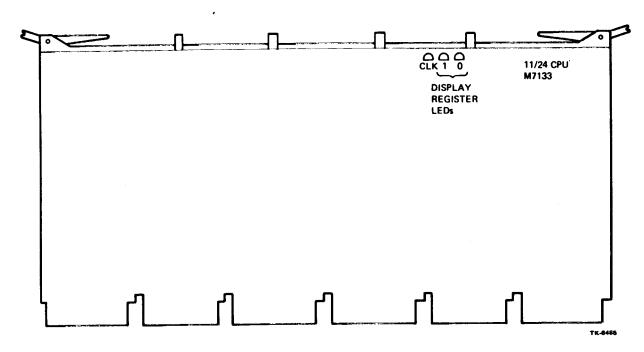

| 2.8.1     | CPU Module (M7133)                                       | 2-30 |

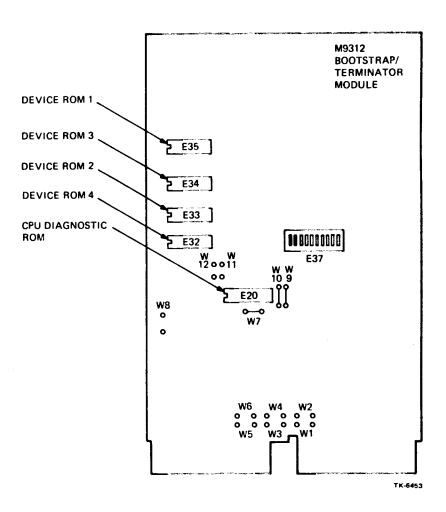

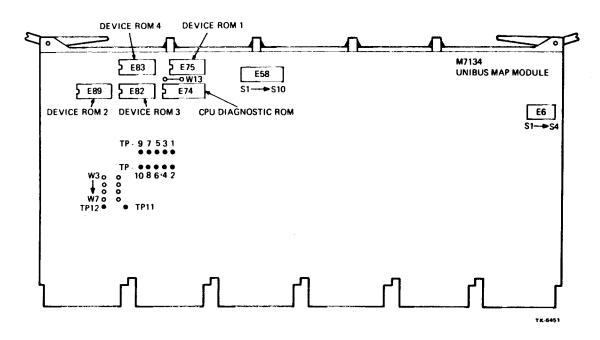

| 2.8.2     | M9312 Bootstrap/Terminator Module                        |      |

| 2.8.2.1   | M9312 Jumper Configuration                               | 2-36 |

| 2.8.2.2   | M9312 ROMs                                               |      |

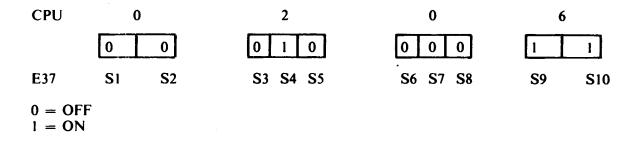

| 2.8.3     | UNIBUS Map Module (M7134)                                |      |

| 2.8.3.1   | UNIBUS Map Module Jumper Leads and Memory Page Selection |      |

| 2.8.3.2   | Diagnostic and Bootstrap Loader ROMs                     |      |

| 2.8.3.3   | Voltage Monitor Switch Selection                         |      |

| 2.9       | INITIAL POWER-UP AND SYSTEM CHECKOUT                     | 2-44 |

| 2.9.1     | Power Check                                              |      |

| 2.9.2     | Power-up                                                 |      |

|           |                                                          |      |

| CHAPTER 3 | PDP-11/24 OPERATION                                      |      |

| 3.1       | CONSOLE OPERATION                                        |      |

| 3.1.1     | Operator's Console Switches                              |      |

| 3.1.2     | Operator's Console Indicators                            |      |

| 3.2       | CONSOLE TERMINAL                                         |      |

| 3.2.1     | ODT Operation                                            |      |

| 3.2.2     | ODT Entry Conditions                                     |      |

| 3.3       | ODT COMMAND SET                                          |      |

| 3.3.1     | Address Specification                                    |      |

| 3.3.2     | Processor I/O Addresses                                  |      |

| 3.3.3     | Entering of Octal Digits                                 |      |

| 3.3.4     | ODT Time-Out                                             |      |

| 3.3.5     | Memory Parity Errors                                     |      |

| 3.3.6     | Invalid Characters                                       |      |

| 3.3.7     | Correcting Type-In Errors                                | 3-12 |

| 3.4       | PDP-11/24 REGISTERS                                      |      |

| 3.4.1     | Processor Status Word                                    | 3-12 |

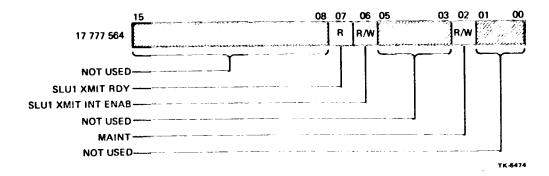

| 3.4.2     | Serial Line Unit 1 Registers                             | 3-14 |

| 3.4.2.1   | SLU1 Receiver Control/Status Register (RCSR)             | 3-14 |

| 3.4.2.2   | SLU1 Receiver Data Buffer (RBUF)                         | 3-14 |

| 3.4.2.3   | SLU1 Transmitter Control/Status Register (XCSR)          | 3-15 |

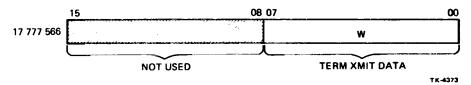

| 3.4.2.4   | SLU1 Transmitter Buffer Register (XBUF)                  | 3-16 |

| 3.4.3     | Serial Line Unit 2 Registers                             | 3-17 |

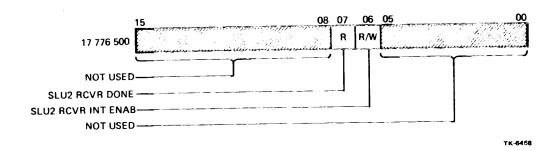

| 3.4.3.1   | SLU2 Receiver Control/Status Register (RCSR)             | 3-17 |

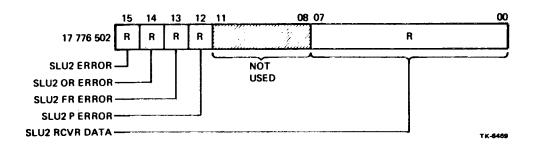

| 3.4.3.2   | SLU2 Receiver Buffer Register (RBUF)                     | 3-18 |

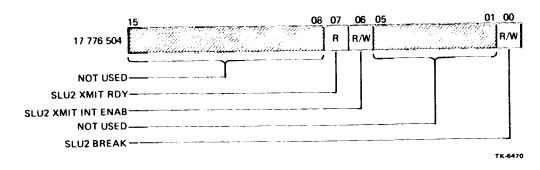

| 3.4.3.3   | SLU2 Transmitter Control/Status Register (XCSR)          | 3-19 |

|          |              |                                               | Page                          |

|----------|--------------|-----------------------------------------------|-------------------------------|

|          |              |                                               |                               |

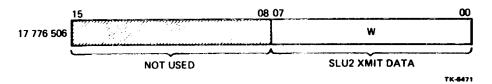

|          | 3.4.3.4      | SLU2 Transmitter Data Buffer Register (XBUF)  | 3-20                          |

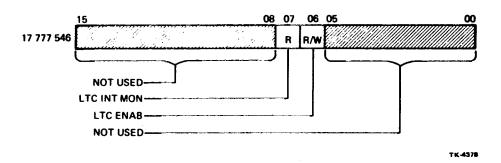

| _        | 3.4.4        | Line Time Clock Control/Status Register (LTC) | 3-20                          |

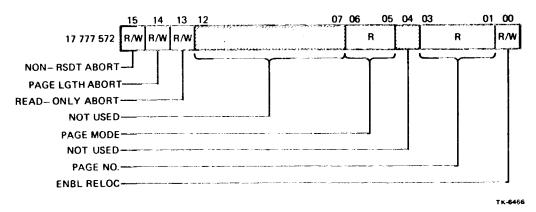

|          | 3.4.5        | Memory Management Registers                   | 3-21                          |

|          | 3.4.5.1      | Status Register 0 (SR0)                       | 3-21                          |

|          | 3.4.5.2      | Status Register 1 (SR1)                       | 3-22                          |

|          | 3.4.5.3      | Status Register 2 (SR2)                       | 3-22                          |

|          | 3.4.5.4      | Status Register 3 (SR3)                       | 3-23                          |

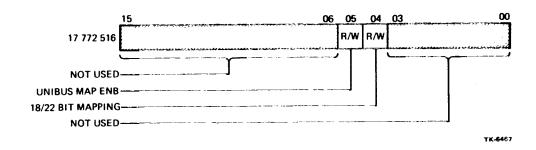

| <b>-</b> | 3.4.6        | Display Register                              | 3-23                          |

| _        | CHAPTER 4    | CPU FUNCTIONAL DESCRIPTION                    |                               |

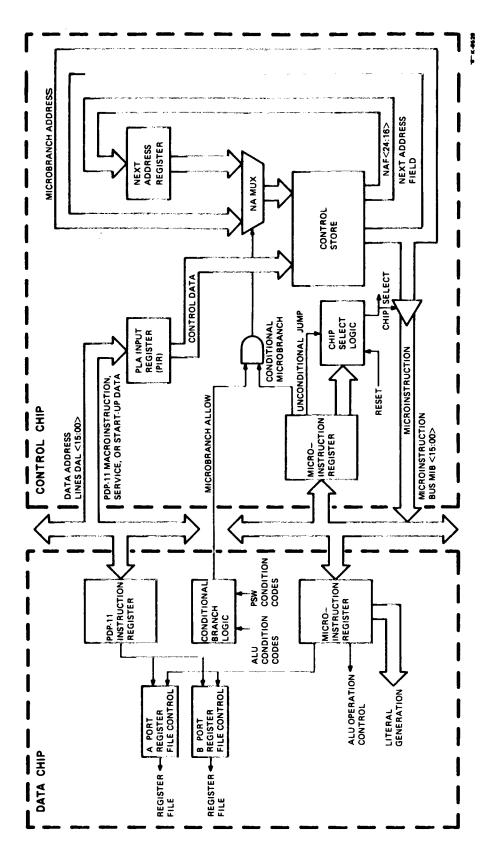

|          | 4.1          | INTRODUCTION                                  | 4-1                           |

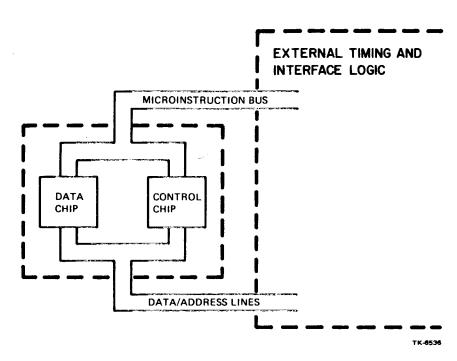

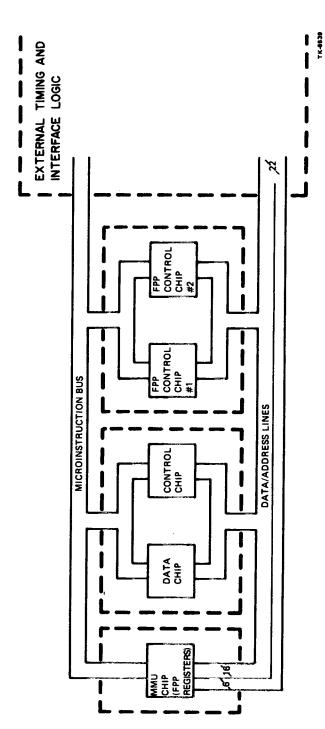

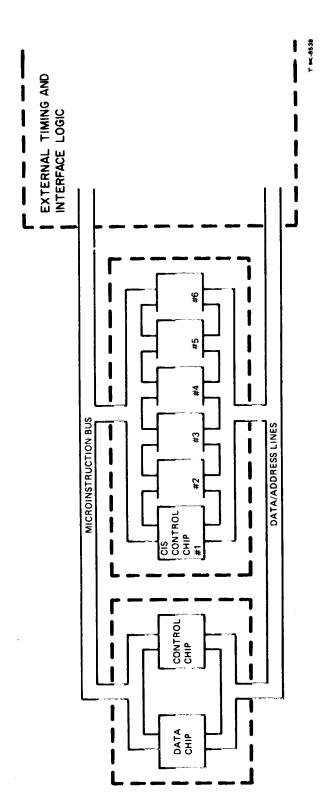

| -        | 4.1.1        | Central Processing Unit                       | 4-1                           |

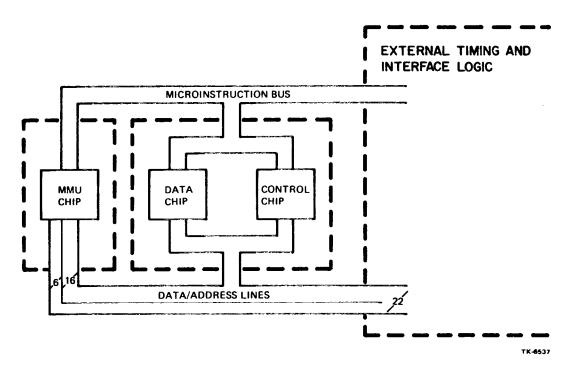

|          | 4.1.2        | Processor Options                             | 4-1                           |

|          | 4.1.2.1      | Memory Management Unit                        | 4-1                           |

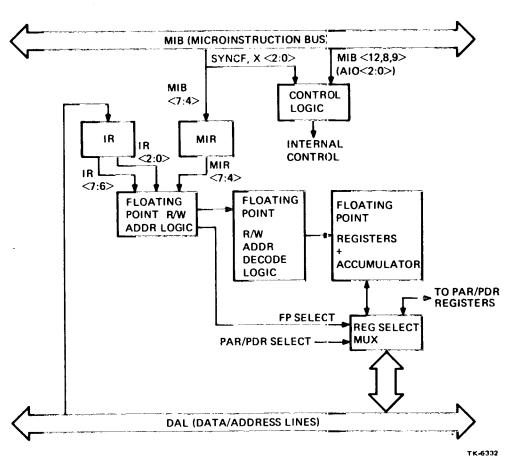

| _        | 4.1.2.2      | Floating-Point Processor                      | 4-3                           |

|          | 4.1.2.3      | Commercial Instruction Set                    | 4-3                           |

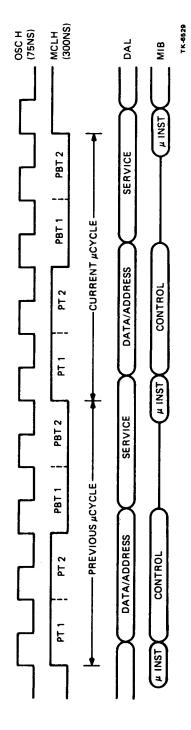

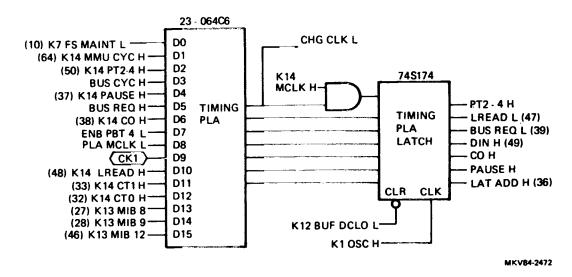

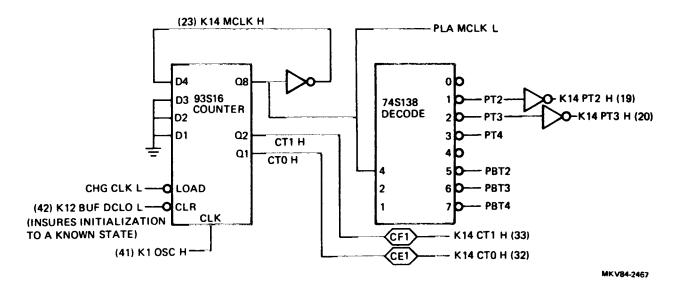

|          | 4.1.2.3      | TIMING                                        | 4-3                           |

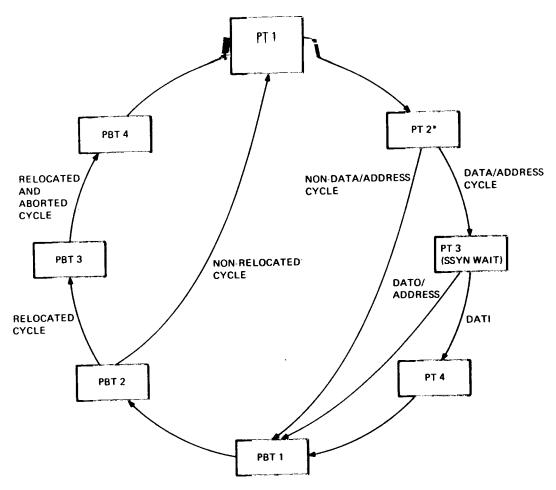

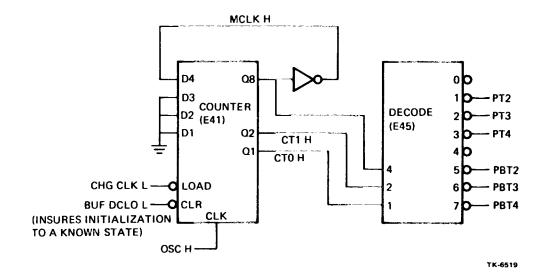

| <b>-</b> | 4.2.1        | Timing Cycles                                 | 4-7                           |

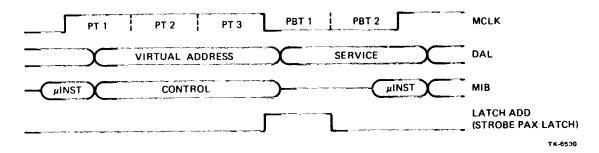

|          | 4.2.1.1      | Short Cycle                                   | 4-7                           |

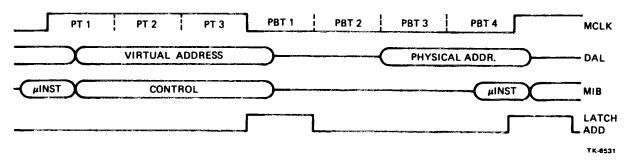

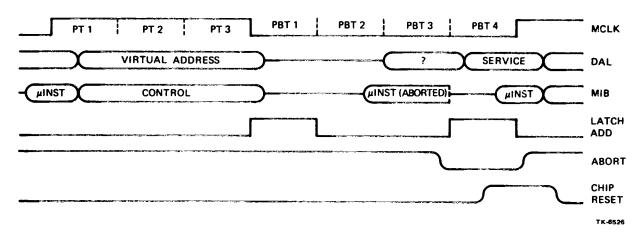

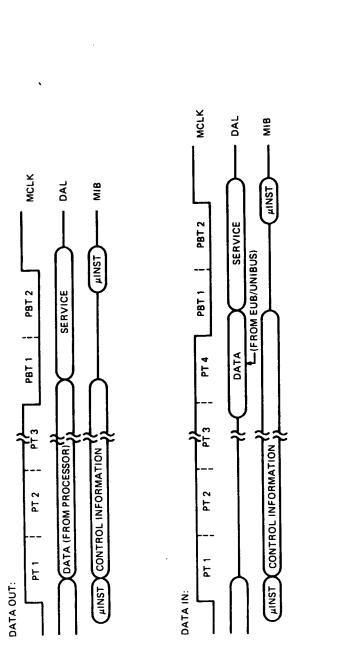

|          | 4.2.1.2      | Input/Output Cycles                           | 4-9                           |

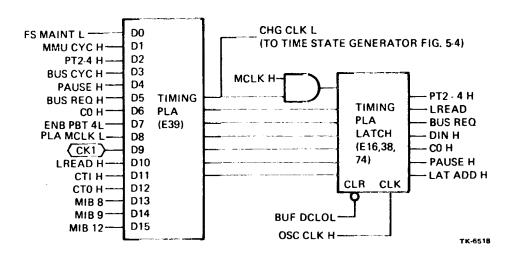

|          | 4.2.2        | Timing Logic                                  | 4-12                          |

|          | 4.2.2        | PDP-11/24 CENTRAL PROCESSING UNIT             | 4-14                          |

|          | 4.3<br>4.3.1 | Control Path                                  | 4-14                          |

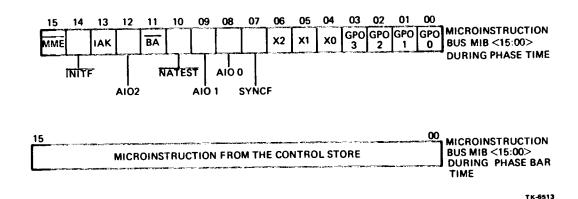

|          |              | Microinstruction Bus (MIB<15:00>)             | 4-19                          |

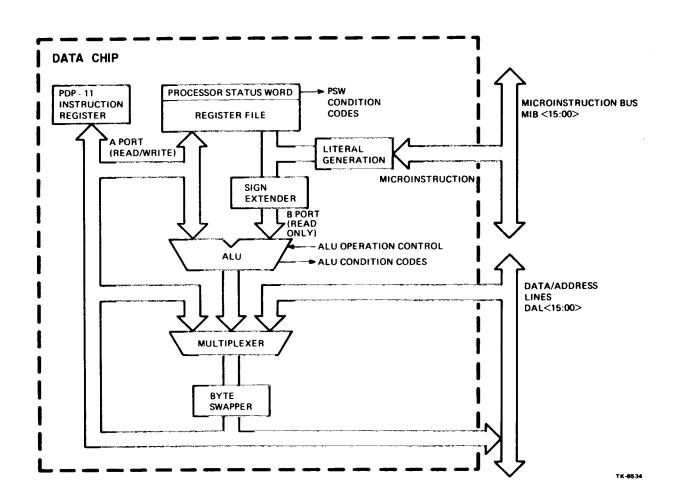

| _        | 4.3.2        | PDP-11/24 Data Path                           | 4-22                          |

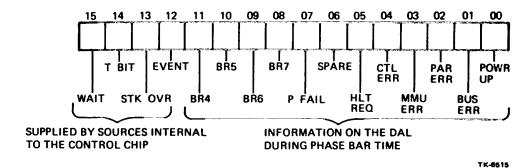

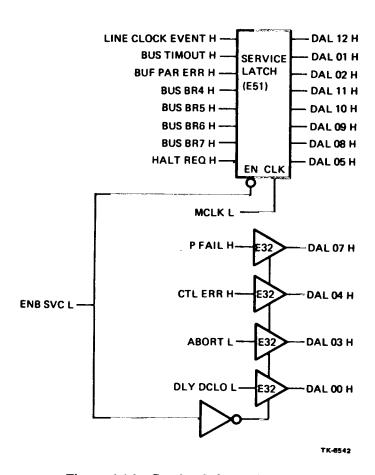

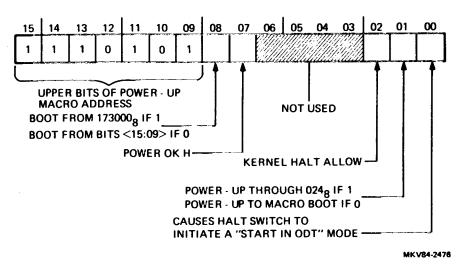

|          | 4.3.3        | Data Address Lines (DAL<15:00>)               | 4-23                          |

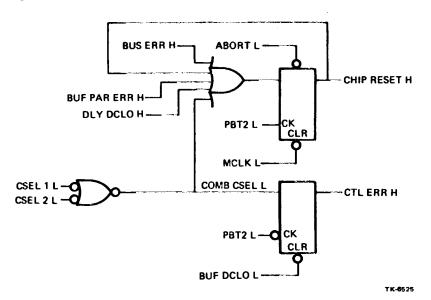

|          | 4.3.4        | PDP-11/24 CHIP SET CONTROL LOGIC              | 4-23                          |

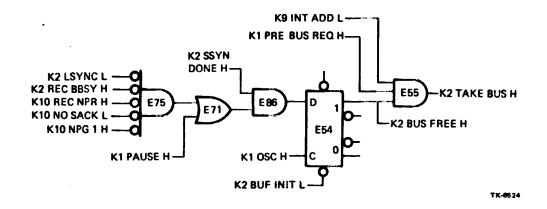

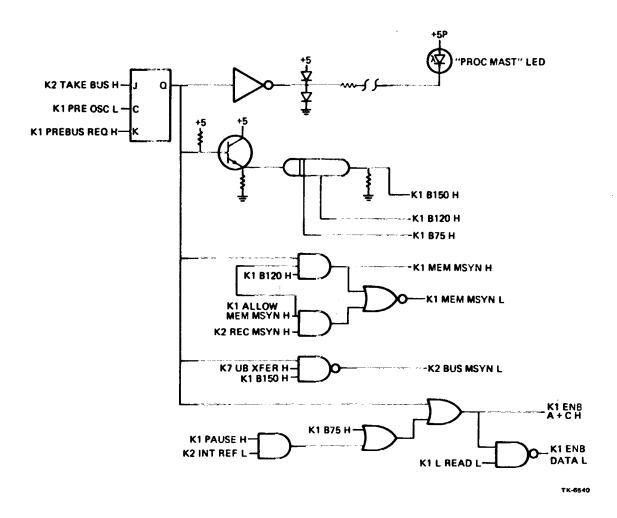

|          | 4.4          | SYSTEM BUS LOGIC                              | 4-24                          |

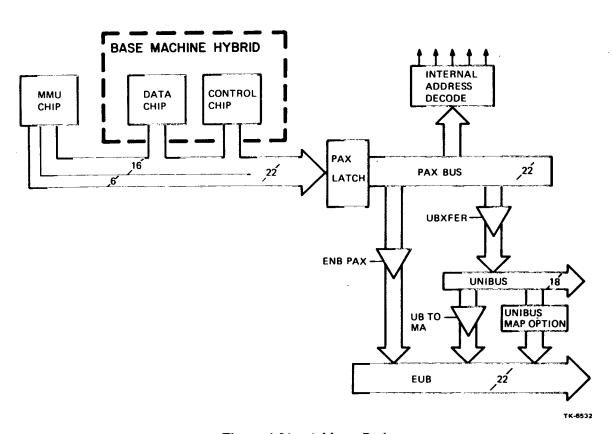

|          | 4.5          | Address and Data                              | 4-24                          |

|          | 4.5.1        | Address and Data                              | 4-24                          |

| _        | 4.5.1.1      | Address                                       |                               |

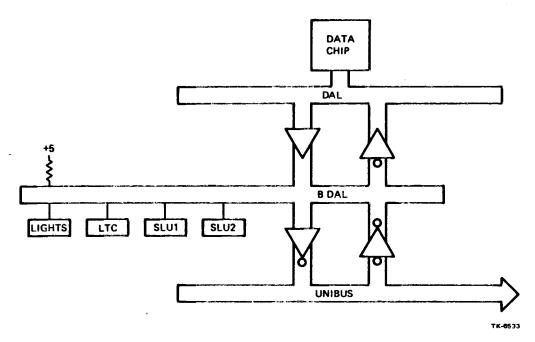

|          | 4.5.1.2      | Data Paths                                    | 4-25<br>1-26                  |

|          | 4.5.1.3      | Direct Memory Access                          | 4-20 مر<br>1-26               |

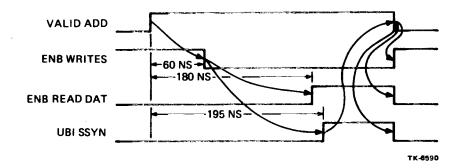

| -        | 4.5.2        | System Bus Timing                             | 4-20 مر<br>4-20               |

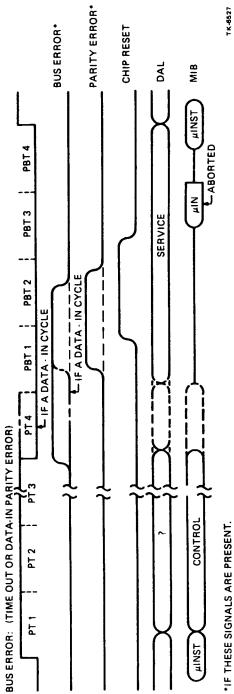

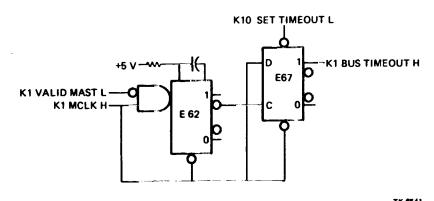

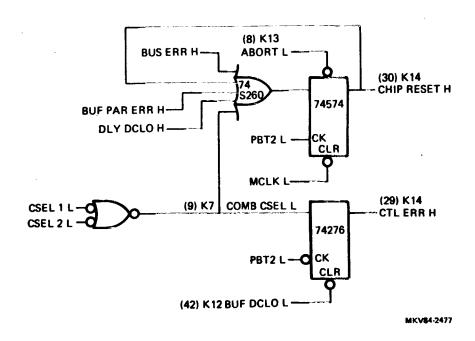

|          | 4.5.3        | System Bus Errors                             | 4-40                          |

|          | 4.5.3.1      | Time-Out Error                                | 4-20 مع- <del>14</del><br>4 م |

| _        | 4.5.3.2      | Parity Error                                  | 4-27 مرتب<br>10 م             |

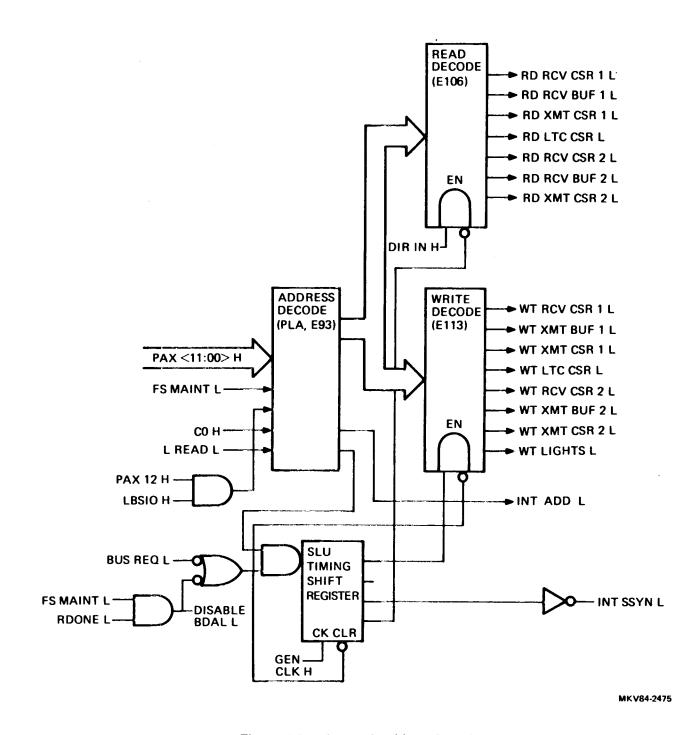

|          | 4.6          | INTERNAL ADDRESS DECODE                       | <del>4-</del> 27 4-27<br>4 20 |

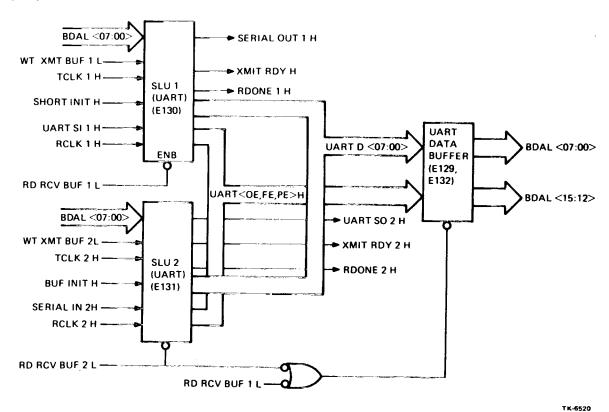

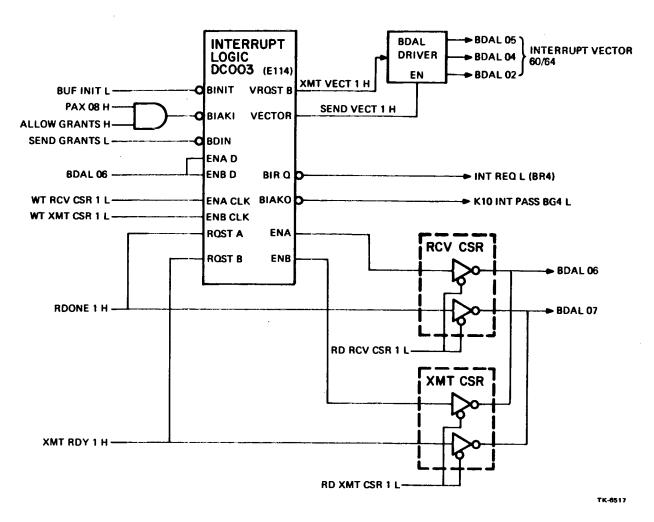

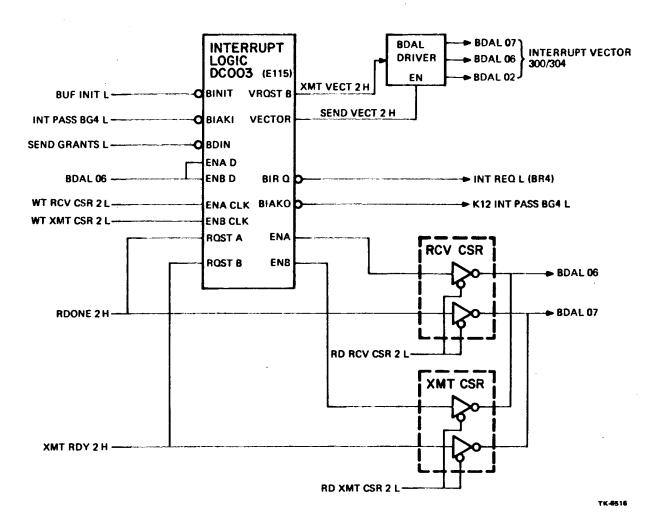

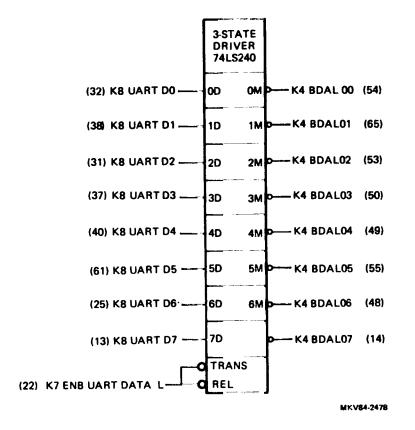

|          | 4.7          | SERIAL LINE UNITS                             | 4-32                          |

| _        | 4.7.1        | Console Terminal SLU                          | 4-32<br>4 27                  |

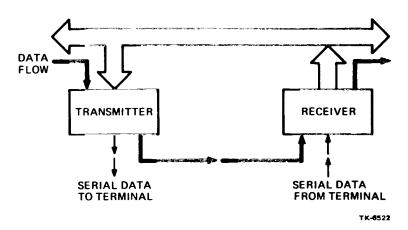

|          | 4.7.1.1      | Transmitter Operation                         | 4-32<br>4 33                  |

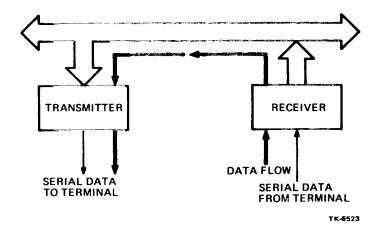

|          | 4.7.1.2      | Receiver Operation                            | 4-33                          |

|          | 4.7.1.3      | SLU1 Maintenance Configuration                | 4-34                          |

|          | 4.7.2        | Serial Line Unit 2                            | 4-33                          |

|          | 4.7.2.1      | Transmitter Operation (SLU2)                  | 4-35                          |

| -        | 4.7.2.2      | SLU2 Receiver Operation                       | 4-35                          |

|          | 4.7.3        | Baud Rate Logic                               | 4-33                          |

|          |              |                                               |                               |

|            |                                      | Page |

|------------|--------------------------------------|------|

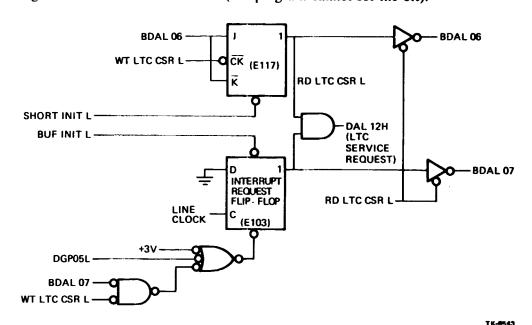

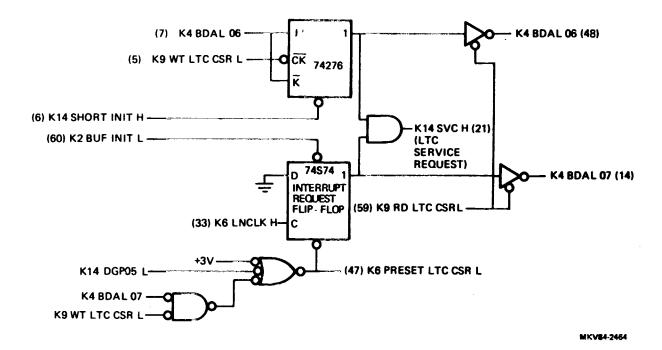

| 4.0        | LINE TIME CLOCK (LTC)                | 1.36 |

| 4.8<br>4.9 | DISPLAY REGISTER                     |      |

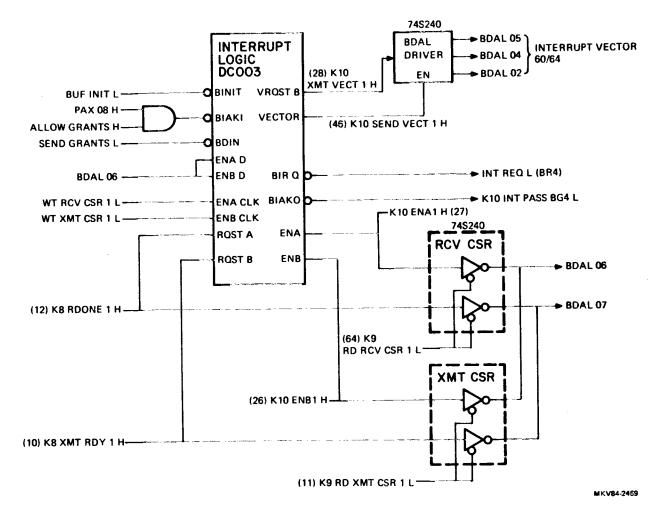

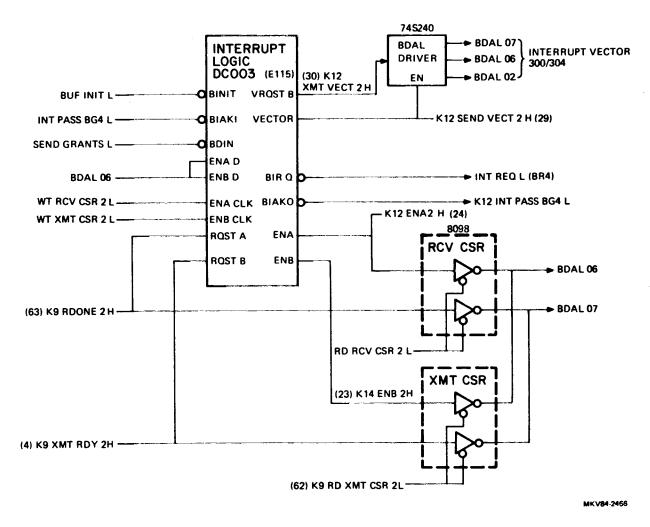

| 4.10       | INTERRUPT REQUEST LOGIC              |      |

| 4.10       | INTERRUPT ERRORS                     |      |

| 4.11.1     | SACK Time-Out                        |      |

| 4.11.2     | Vector Time-Out                      |      |

| CHAPTER 5  | MEMORY MANAGEMENT                    |      |

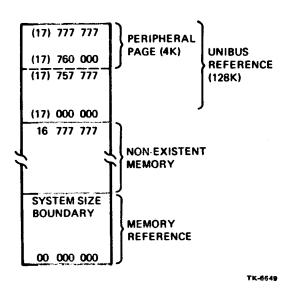

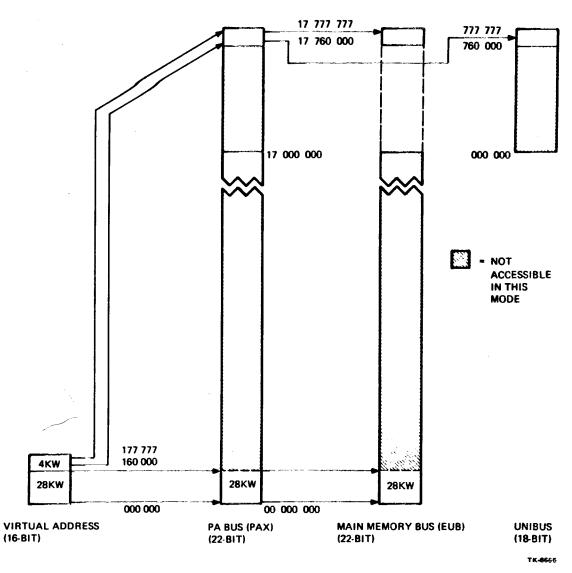

| 5.1        | INTRODUCTION                         | 5-1  |

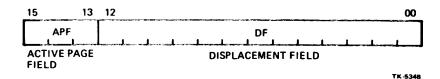

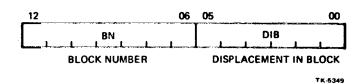

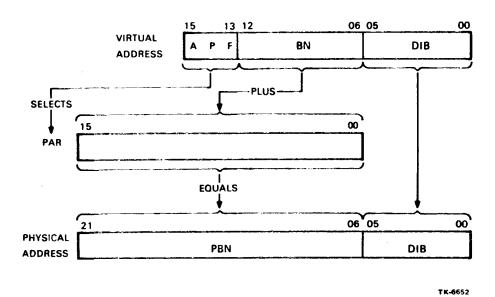

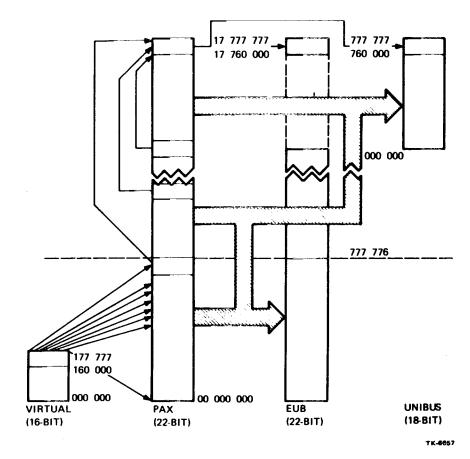

| 5.2        | RELOCATION                           | 5-2  |

| 5.2.1      | Address Mapping                      |      |

| 5.2.2      | Address Translation                  | 5-9  |

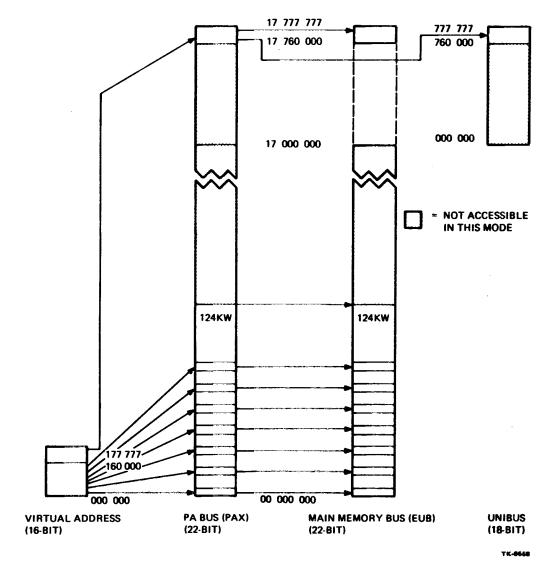

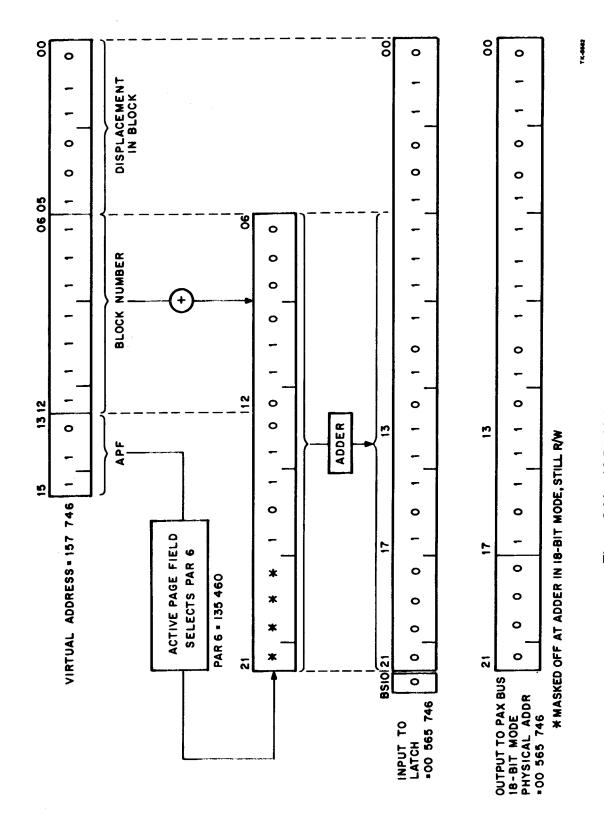

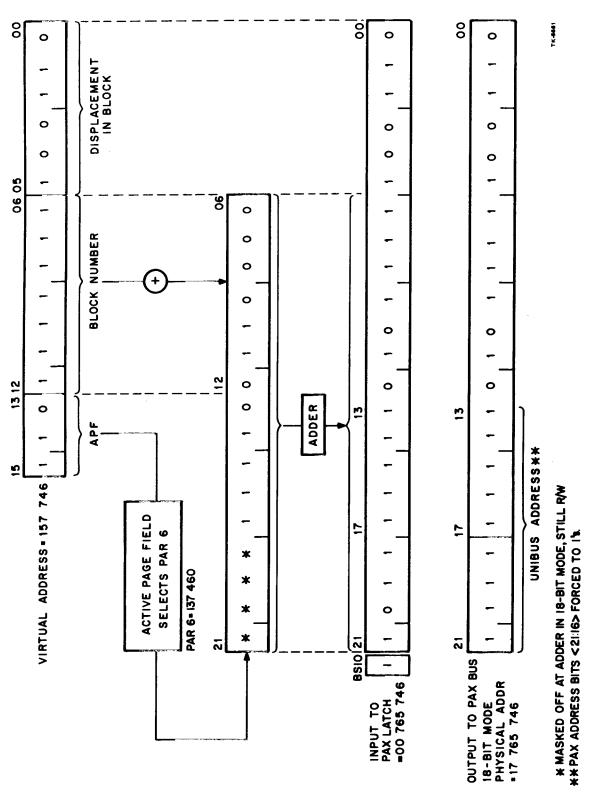

| 5.2.2.1    | 18-Bit Mapping                       | 5-9  |

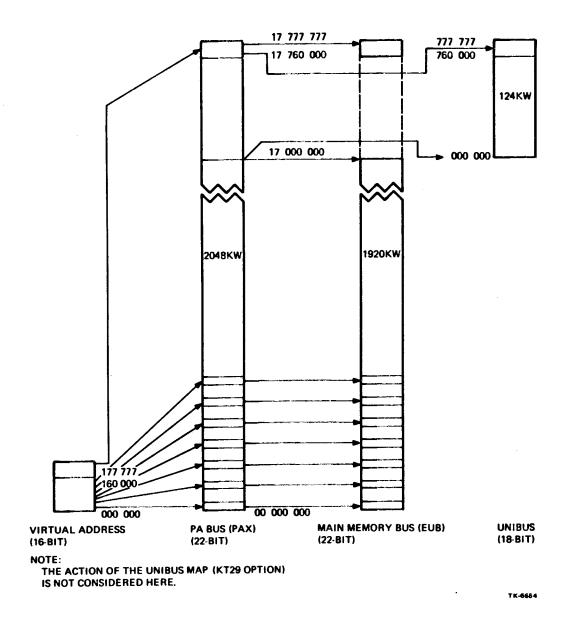

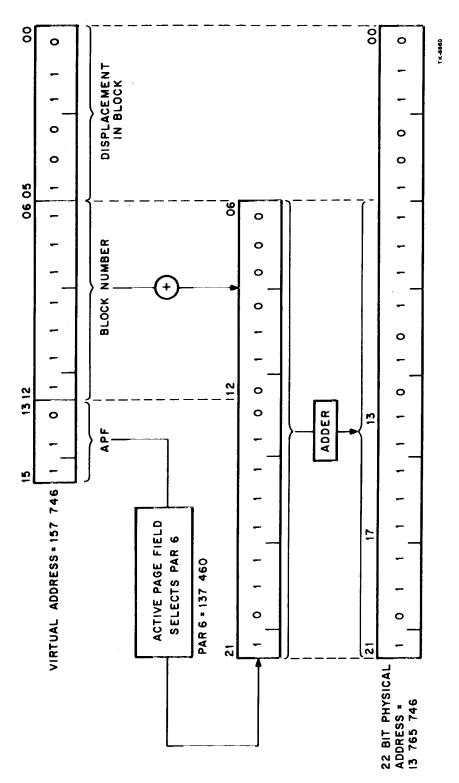

| 5.2.2.2    | 22-Bit Mapping                       |      |

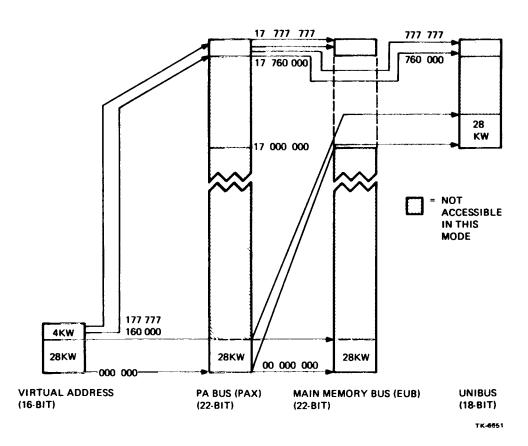

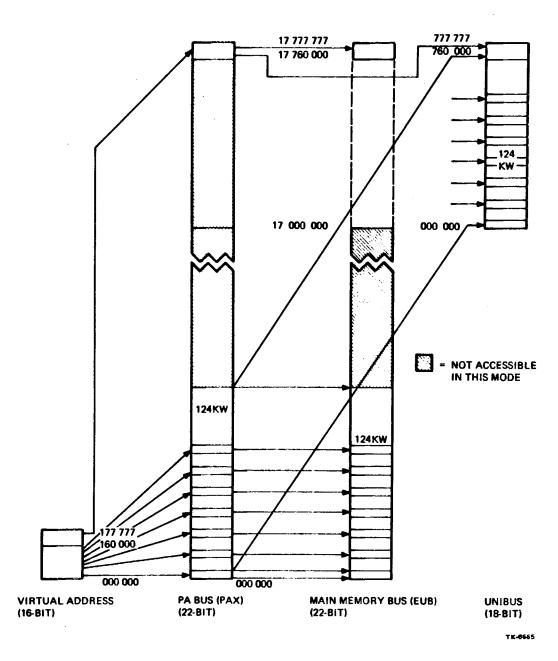

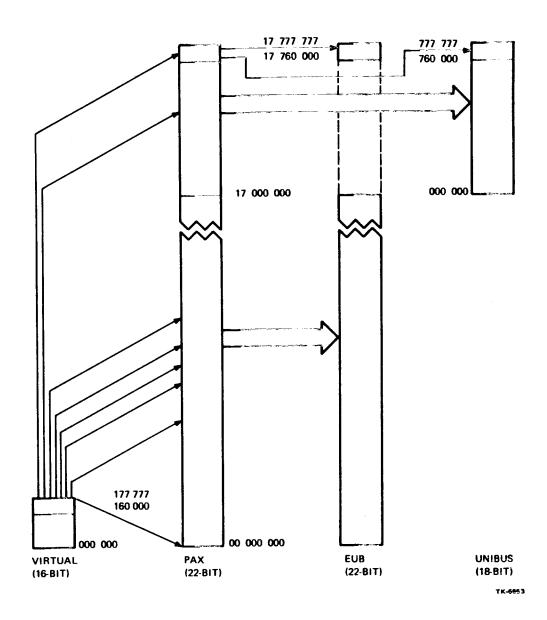

| 5.2.2.3    | Physical Addressing                  | 5-13 |

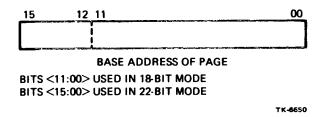

| 5.3        | MEMORY MANAGEMENT REGISTERS          |      |

| 5.3.1      | Page Address Register (PAR)          | 5-18 |

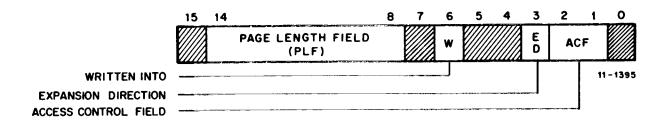

| 5.3.2      | Page Descriptor Registers (PDR)      | 5-18 |

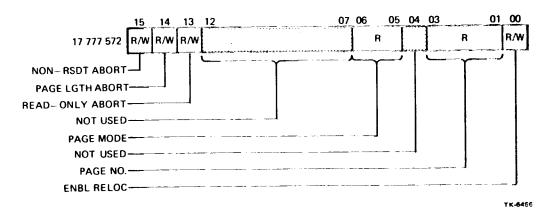

| 5.4        | MEMORY MANAGEMENT STATUS REGISTERS   |      |

| 5.4.1      | Status Register 0 (SR0)              |      |

| 5.4.2      | Status Register 1 (SR1)              |      |

| 5.4.3      | Status Register 2 (SR2)              | 5-22 |

| 5.4.4      | Status Register 3 (SR3)              | 5-22 |

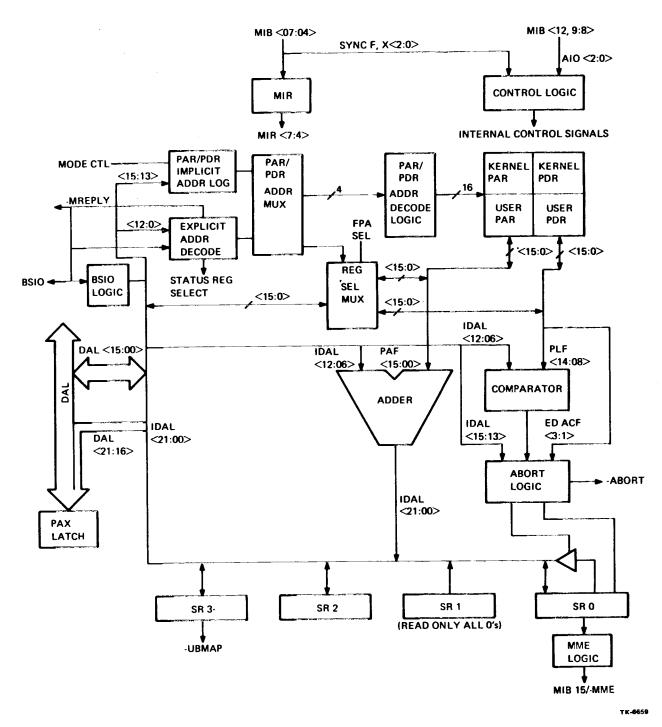

| 5.5        | MICROINSTRUCTION REGISTER (MIR)      |      |

| 5.6        | MEMORY MANAGEMENT ENABLE (MME) LOGIC |      |

| 5.7        | MEMORY MANAGEMENT TIMING             | 5-22 |

| 5.8        | MEMORY MANAGEMENT CONTROL SIGNALS    | 5-23 |

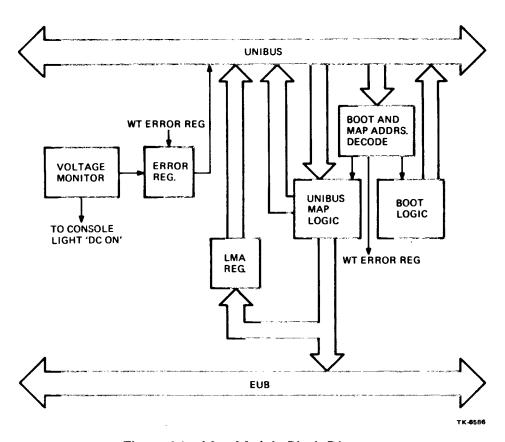

| CHAPTER 6  | KT24 UNIBUS MAP OPTION               |      |

| 6.1        | INTRODUCTION                         |      |

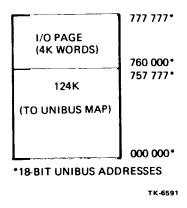

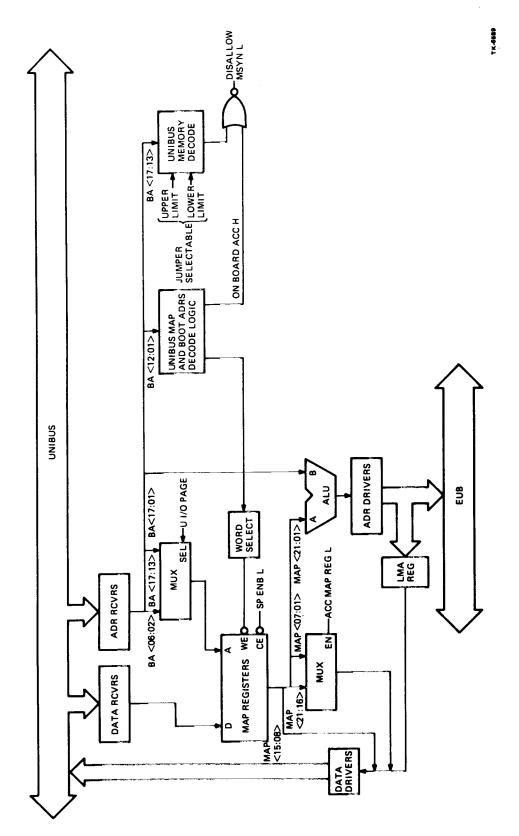

| 6.2        | UNIBUS MAP                           |      |

| 6.2.1      | MSYN Steering                        |      |

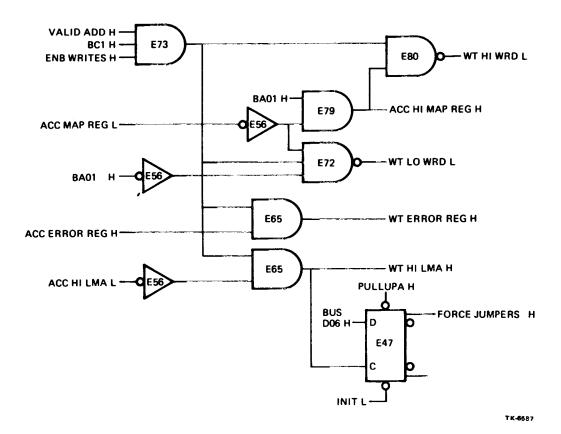

| 6.2.2      | Map Control                          |      |

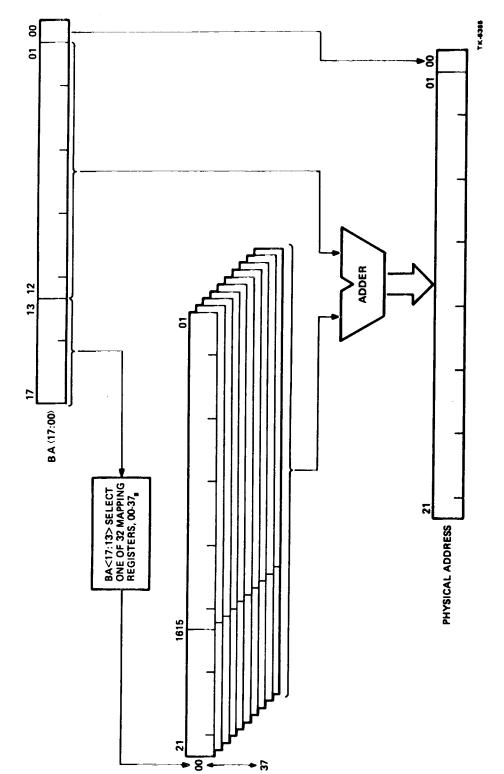

| 6.2.3      | Map Addressing and Relocation        |      |

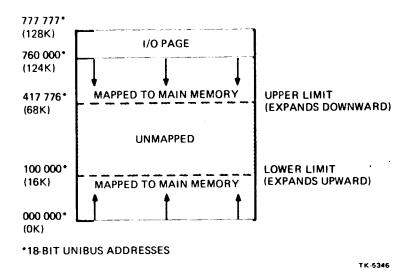

| 6.2.4      | Addressing Limits                    |      |

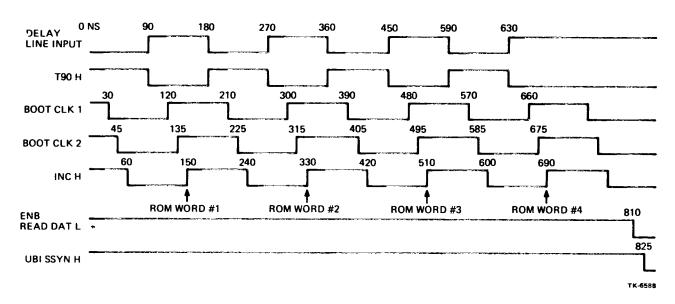

| 6.3        | BOOT LOGIC                           |      |

| 6.4        | VOLTAGE MONITOR                      |      |

| 6.5        | REGISTERS                            |      |

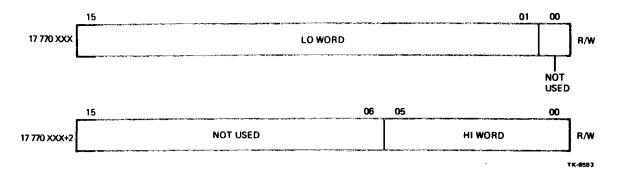

| 6.5.1      | UNIBUS Map Registers                 |      |

| 6.5.2      | Last Mapped Address (LMA) Register   |      |

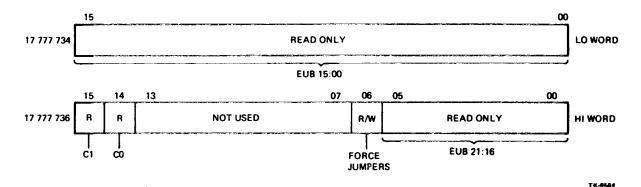

| 6.5.3      | CPU Error Register                   | 6-11 |

Page

| CHAPTER 7                | FLOATING-POINT PROCESSOR FUNCTIONAL DESCRIPTION                       |           |

|--------------------------|-----------------------------------------------------------------------|-----------|

| 7.1                      | INTRODUCTION                                                          |           |

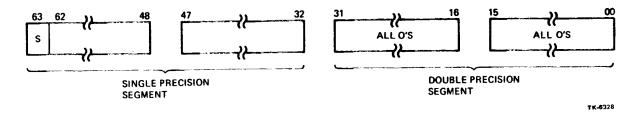

| 7.2                      | FLOATING-POINT FORMATS                                                |           |

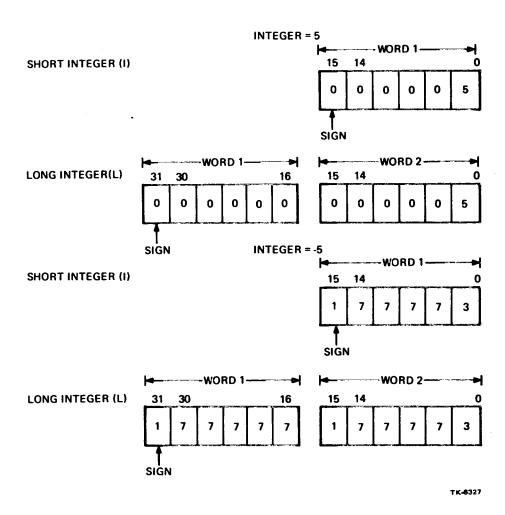

| 7.2.1                    | FPP Integer Formats                                                   |           |

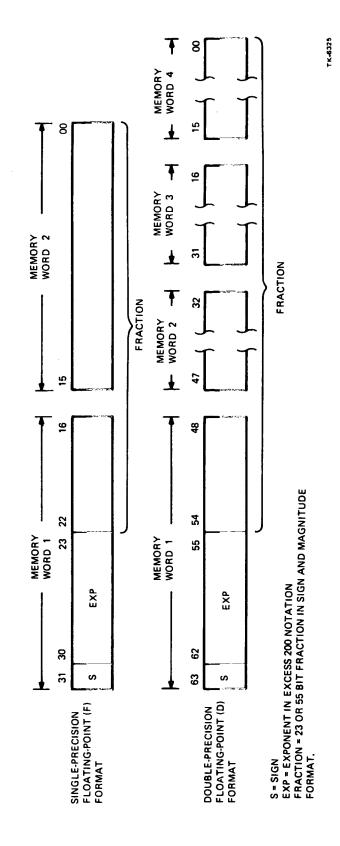

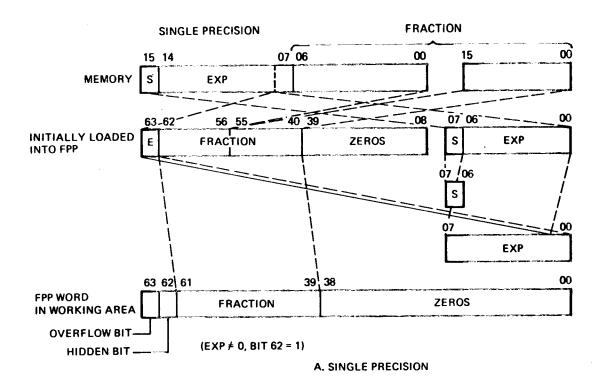

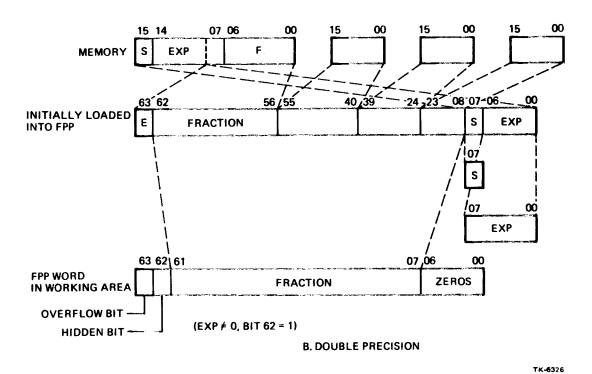

| 7.2.2                    | FPP Precision Formats                                                 |           |

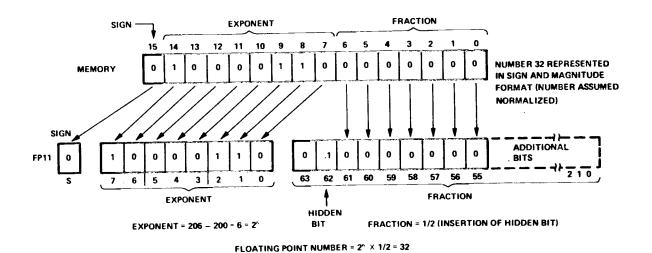

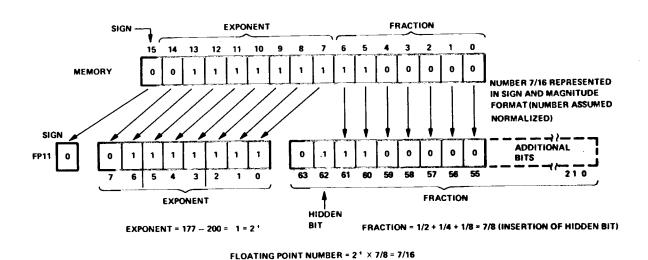

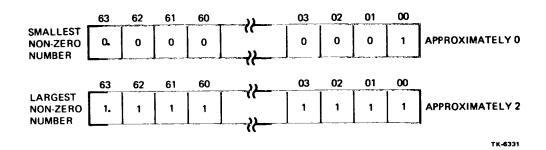

| 7.2.3                    | Floating-Point Data Word                                              |           |

| 7.2.3<br>7.2.3.1         | Floating-Point Fraction                                               |           |

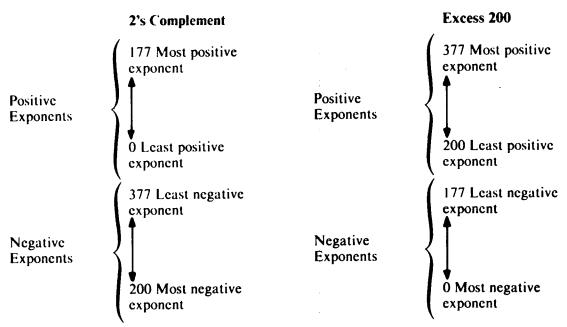

| 7.2.3.1                  | Floating-Point Exponent                                               |           |

| 7.2.3.2<br>7.2. <b>4</b> | Processing of Floating-Point Exceptions                               |           |

| 7.2.4                    | FLOATING-POINT PROCESSOR STATUS REGISTER (FPS)                        |           |

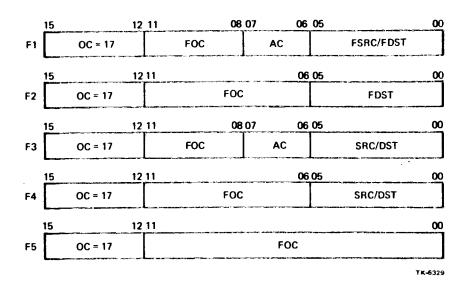

| 7.3<br>7.4               | FLOATING-POINT INSTRUCTION FORMATS                                    |           |

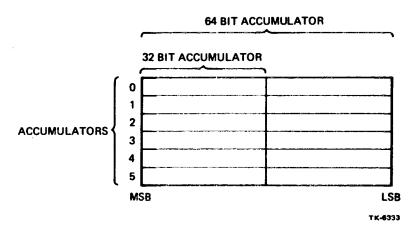

|                          | Floating-Point Accumulators                                           |           |

| 7.4.1                    | Instruction Formats                                                   |           |

| 7.4.2                    | FLOATING-POINT INSTRUCTIONS                                           |           |

| 7.5                      | Arithmetic Instructions                                               |           |

| 7.5.1                    | Floating-Modulo Instruction                                           |           |

| 7.5.2                    | Load Instruction                                                      |           |

| 7.5.3                    | Store Instruction                                                     | ••••      |

| 7.5.4                    | Load Convert (Double-to-Floating, Floating-to-Double) Instructions    | ••••      |

| 7.5.5                    | Store Convert (Double-to-Floating, Floating-to-Double) Instructions   | ••••      |

| 7.5.6                    | Clear Instruction                                                     | • • • • • |

| 7.5.7                    | Test Instruction                                                      | ••••      |

| 7.5.8                    | lest instruction                                                      | • • • • • |

| 7.5.9                    | Absolute Instruction                                                  | ••••      |

| 7.5.10                   | Negate Instruction                                                    | ••••      |

| 7.5.11                   | Load Exponent Instruction                                             | ••••      |

| 7.5.12                   | Load Convert Integer-to-Floating Instruction                          | ••••      |

| 7.5.13                   | Store Exponent Instruction                                            | ••••      |

| 7.5.14                   | Store Convert Floating-to-Integer Instruction                         | • • • •   |

| 7.5.15                   | Load FPP's Program Status Instruction                                 | ••••      |

| 7.5.16                   | Store FPP's Program Status Instruction                                | ••••      |

| 7.5.17                   | Store FPP's Status Instruction                                        | • • • •   |

| 7.5.18                   | Copy Floating Condition Codes Instruction                             | ••••      |

| 7.5.19                   | Set Floating Mode Instruction                                         | ••••      |

| 7.5.20                   | Set Double Mode Instruction                                           | ••••      |

| 7.5.21                   | Set Integer Mode Instruction                                          | ••••      |

| 7.5.22                   | Set Long-Integer Mode InstructionFLOATING-POINT INSTRUCTION EXECUTION | ••••      |

| 7.6                      | FLOATING-POINT INSTRUCTION EXECUTION                                  | ••••      |

| CHAPTER 8                | COMMERCIAL INSTRUCTION SET PROCESSOR                                  |           |

| 8.1                      | INTRODUCTION                                                          | ••••      |

| 8.2                      | CHARACTER DATA TYPES                                                  | ••••      |

| 8.3                      | DECIMAL STRING DATA TYPES                                             | ••••      |

| 8.4                      | CIS INSTRUCTION EXECUTION                                             | ••••      |

Page

| CHAPTER 9   | MAINTENANCE                                          |              |

|-------------|------------------------------------------------------|--------------|

| 9.1         | TROUBLESHOOTING PROCEDURES                           | <b>9-</b> 1  |

| 9.2         | MAINDEC DIAGNOSTIC PROGRAMS                          | 9-12         |

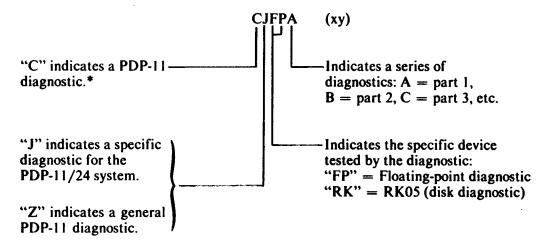

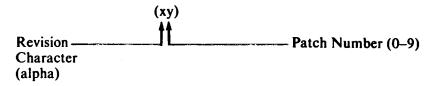

| 9.2.1       | Diagnostic Designations                              |              |

| 9.2.2       | Running Diagnostics                                  | 9-13         |

| 9.2.2.1     | CJKDB - PDP-11/24 CPU Diagnostic                     | <b>9-1</b> 3 |

| 9.2.2.2     | CJKDA - KTF11-A Memory Management Diagnostic         | 9-14         |

| 9.2.2.3     | CJKDF - II/24 Option Diagnostic                      | 9-14         |

| 9.2.2.4     | CZM9B - M9312, 11/24, 11/44 UBI Boot Diagnostic      | 9-14         |

| 9.2.2.5     | CKKUA - 11/24, 11/44 UBI Map Diagnostic              | 9-15         |

| 9.2.2.6     | CZMSP - MS11P Memory Diagnostic                      | 9-15         |

| 9.2.2.7     | DZKAQ - PDP-11 Power-Fail Diagnostic                 | 9-15         |

| 9.2.2.8     | CKJDC, CJKDD - KEF11-A FPP Diagnostic Part 1 and 2   | 9-16         |

| 9.2.2.9     | CJKDH - KEF11-B CISP Diagnostic                      | 9-16         |

|             |                                                      |              |

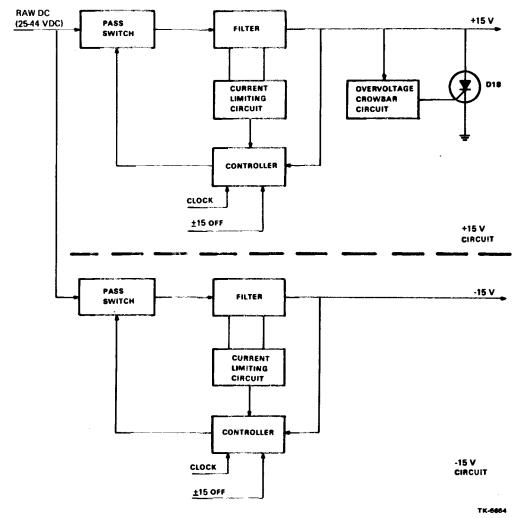

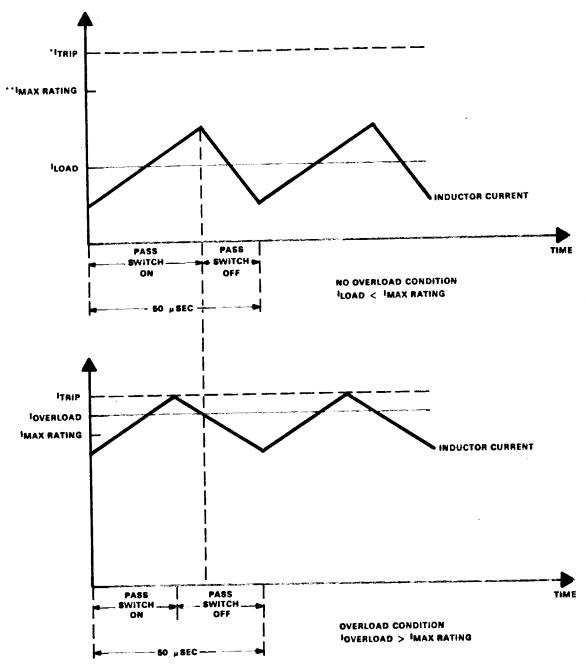

| APPENDIX A  | COMMUNICATIONS REGULATOR                             |              |

| A.1         | FUNCTIONAL DESCRIPTION                               | <b>A-</b> 1  |

| A.2         | +15 V CIRCUIT DETAILED DESCRIPTION                   |              |

| A.3         | -15 V CIRCUIT DETAILED DESCRIPTION                   |              |

| APPENDIX B  | FPP INSTRUCTION SET                                  |              |

| APPENDIX C  | PDP-11/24 BACKPLANE ASSIGNMENTS                      |              |

| C.1         | MODULE UTILIZATION                                   | C-1          |

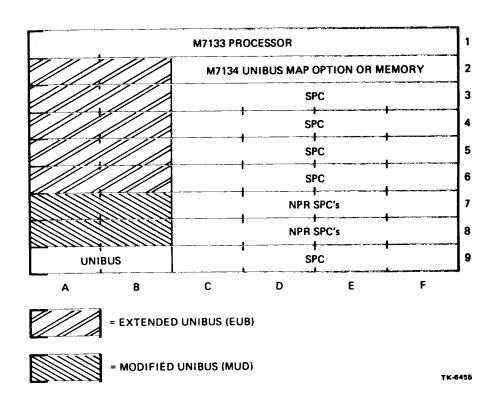

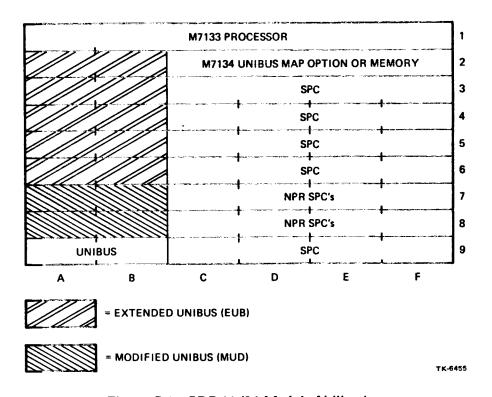

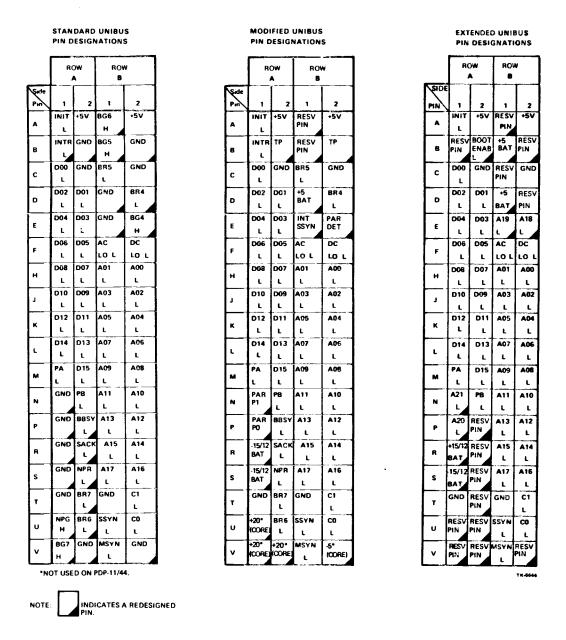

| C.2         | STANDARD, MODIFIED, AND EXTENDED BACKPLANE           |              |

|             | STANDARD, MODIFIED, AND EXTENDED BACKPLANE LOCATIONS | C-2          |

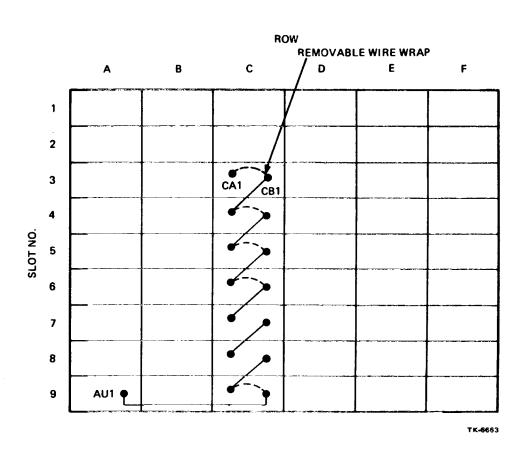

| C.3         | SPC BACKPLANE LOCATIONS                              | <b>C</b> -3  |

| C.4         | NPG JUMPER LEAD ROUTING                              | <b>C</b> -4  |

| APPENDIX D  | PDP-11/24 CPU MODIFICATIONS                          |              |

| · — · · · · |                                                      |              |

| D.1         | INTRODUCTION                                         | D-1          |

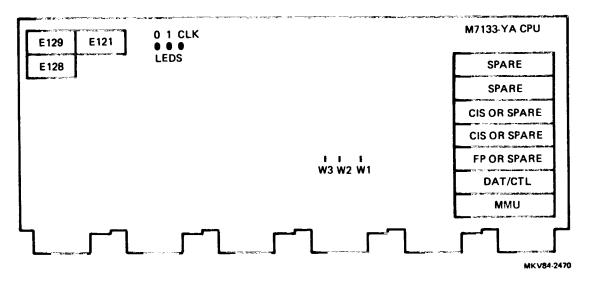

| D.2         | SWITCHES/JUMPERS LOCATION CHANGES FOR M7133-YA       | D-1          |

| D.3         | INTERNAL GATE ARRAY LOGIC (DC369B, DC370B)           |              |

| D.4         | GATE ARRAY PINOUT (DC369B, DC370B)                   | D-9          |

| D.5         | ADDITIONAL GATE ARRAY LOGIC (DC369B, DC370B)         | D-10         |

### **FIGURES**

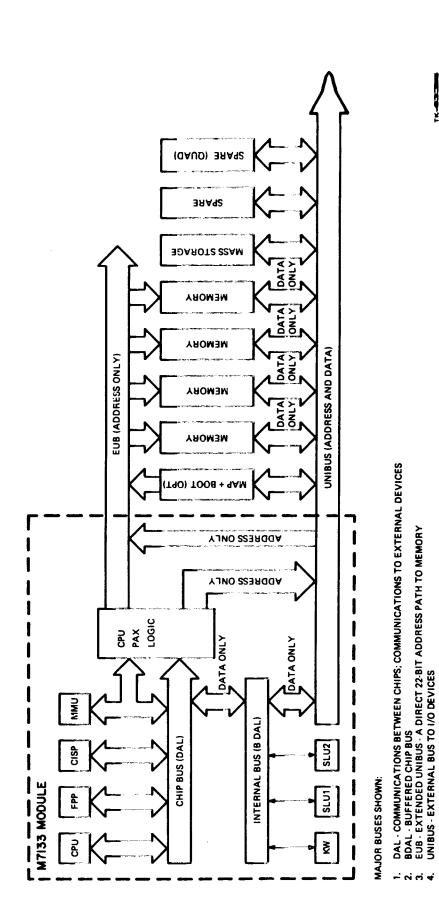

| 1-1 PDP-11/24 System Block Diagram 1-2 PDP-11/24 Central Processing Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 7                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

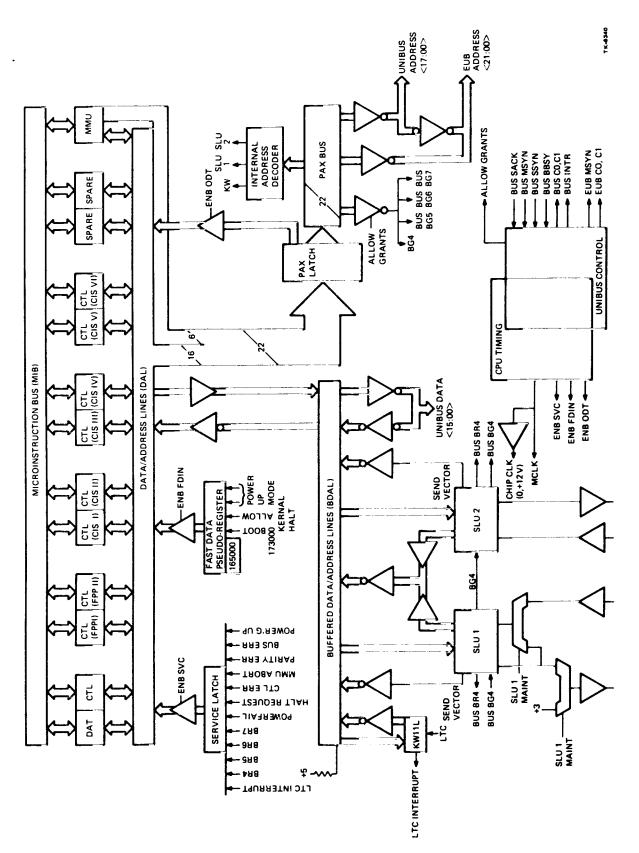

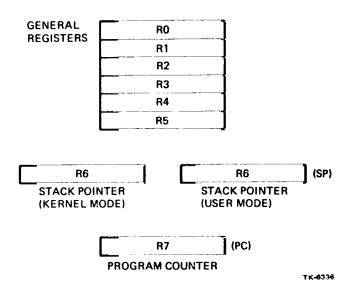

| 1-2 PDP-11/24 Central Processing Unit. 1-3 PDP-11/24 General Registers. 1-4 High and Low Bytes. 1-5 Word and Byte Addressing for the First 4K. 1-6 PDP-11/24 Packaged Systems in an H9645 Cabinet. 1-7 I/O Connector Panels (IOCPs) for H9642/H9645 Cabinets. 2-1 Connector Specifications for BA11-A and BA11-L. 2-2 874-D, -E Connector Specifications. 2-3 PDP-11/24-AA, -AC, -BC Unit Packaging. 2-4 Unpacking a PDP-11/24 System. 2-5 BA11-L Mounting Box. 2-6 Mounting Envelope Installation. 2-7 PDP-11/24 System - CPU Mounting Box Fully Extended. 2-7 PDP-11/24 System - CPU Mounting Box Fully Extended. 2-9 Single-Channel Slide Assembly. 2-10 Designated Mounting Holes for Slide-Mounted PDP-11/24 CPUs Installed in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets. 2-11 Cabinet Slide Installation. 2-12 Mounting Box-to-Slide Installation. 2-13 H9642 (Single-Bay) and H9645 (Wide-Body) Cabinets - Rear View. 2-14 Installing Leveler Feet in the H9642 Cabinet. 2-15 Stabilizer Arm Installation. 2-16 Leveler Feet Adjustment. 2-17 CPU Cabinet - Removing the RFI Shield Panel. | 1 7                  |

| 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

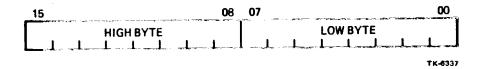

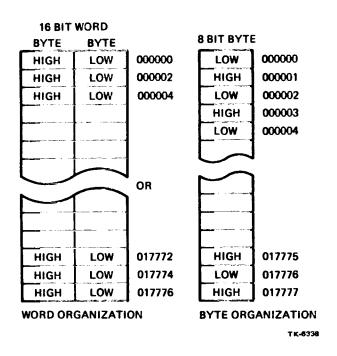

| High and Low Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

| 1-5 Word and Byte Addressing for the First 4K 1-6 PDP-11/24 Packaged Systems in an H9645 Cabinet 1-7 I/O Connector Panels (IOCPs) for H9642/H9645 Cabinets 2-1 Connector Specifications for BA11-A and BA11-L 2-2 874-D, -E Connector Specifications 2-3 PDP-11/24-AA, -AC, -BC Unit Packaging 2-4 Unpacking a PDP-11/24 System 2-5 BA11-L Mounting Box 2-6 Mounting Envelope Installation 2-7 PDP-11/24 System - CPU Mounting Box Fully Extended 2-8 BA11-AA, -AB Mounting Box Index Plate Installation 2-9 Single-Channel Slide Assembly 2-10 Designated Mounting Holes for Slide-Mounted PDP-11/24 CPUs Installed in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets 2-11 Cabinet Slide Installation 2-12 Mounting Box-to-Slide Installation 2-13 H9642 (Single-Bay) and H9645 (Wide-Body) Cabinets - Rear View 2-14 Installing Leveler Feet in the H9642 Cabinet 2-15 Stabilizer Arm Installation 2-16 Leveler Feet Adjustment 2-17 CPU Cabinet - Removing the RFI Shield Panel                                                                                                                     | 1-/                  |

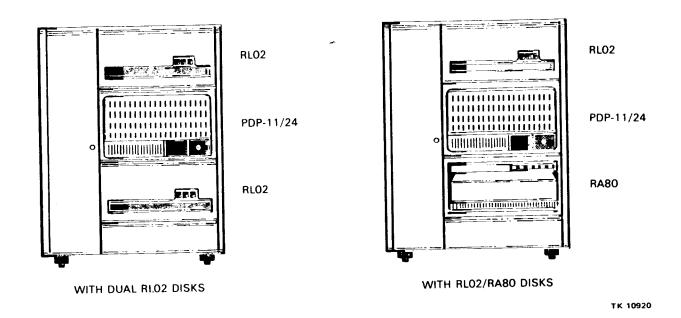

| 1-6 1-7 1/O Connector Panels (IOCPs) for H9642/H9645 Cabinets 2-1 2-1 2-2 874-D, -E Connector Specifications 2-3 PDP-11/24-AA, -AC, -BC Unit Packaging 2-4 Unpacking a PDP-11/24 System 2-5 BA11-L Mounting Box 2-6 Mounting Envelope Installation 2-7 PDP-11/24 System - CPU Mounting Box Fully Extended 2-8 BA11-AA, -AB Mounting Box Index Plate Installation 2-9 Single-Channel Slide Assembly 2-9 Single-Channel Slide Assembly 2-10 Designated Mounting Holes for Slide-Mounted PDP-11/24 CPUs Installed in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets 2-11 Cabinet Slide Installation 2-12 Mounting Box-to-Slide Installation 2-13 H9642 (Single-Bay) and H9645 (Wide-Body) Cabinets - Rear View 2-14 Installing Leveler Feet in the H9642 Cabinet 2-15 Stabilizer Arm Installation 2-16 Leveler Feet Adjustment 2-17 CPU Cabinet - Removing the RFI Shield Panel                                                                                                                                                                                                                           | 1                    |

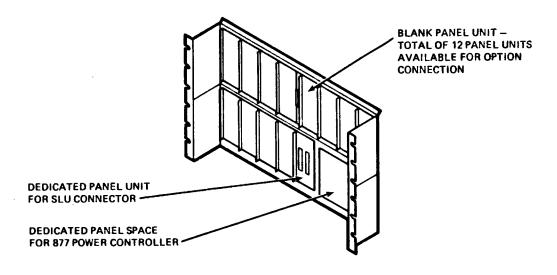

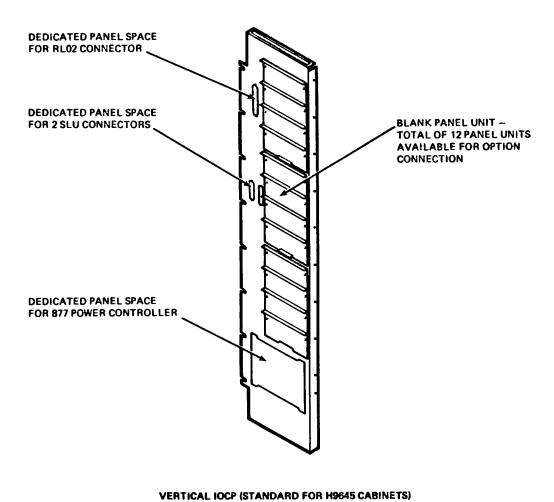

| 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-14                 |

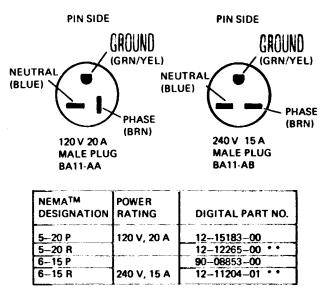

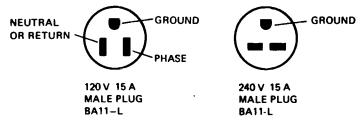

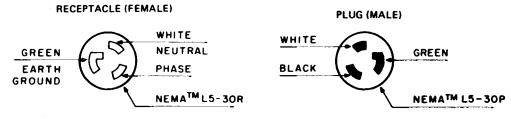

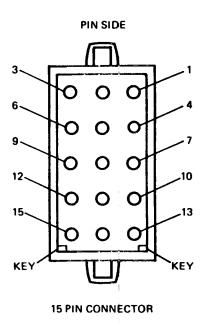

| Connector Specifications for BA11-A and BA11-L 2-2 874-D, -E Connector Specifications 2-3 PDP-11/24-AA, -AC, -BC Unit Packaging Unpacking a PDP-11/24 System 2-5 BA11-L Mounting Box 2-6 Mounting Envelope Installation 2-7 PDP-11/24 System - CPU Mounting Box Fully Extended 2-8 BA11-AA, -AB Mounting Box Index Plate Installation 2-9 Single-Channel Slide Assembly 2-10 Designated Mounting Holes for Slide-Mounted PDP-11/24 CPUs Installed in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets 2-11 Cabinet Slide Installation 2-12 Mounting Box-to-Slide Installation 2-13 H9642 (Single-Bay) and H9645 (Wide-Body) Cabinets - Rear View 2-14 Installing Leveler Feet in the H9642 Cabinet 2-15 Stabilizer Arm Installation 2-16 Leveler Feet Adjustment 2-17 CPU Cabinet Papels in the RFI Shield Panel                                                                                                                                                                                                                                                                                         | 1-13                 |

| 2-2 874-D, -E Connector Specifications 2-3 PDP-11/24-AA, -AC, -BC Unit Packaging 2-4 Unpacking a PDP-11/24 System 2-5 BA11-L Mounting Box 2-6 Mounting Envelope Installation 2-7 PDP-11/24 System - CPU Mounting Box Fully Extended 2-8 BA11-AA, -AB Mounting Box Index Plate Installation 2-9 Single-Channel Slide Assembly 2-10 Designated Mounting Holes for Slide-Mounted PDP-11/24 CPUs Installed in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets 2-11 Cabinet Slide Installation 2-12 Mounting Box-to-Slide Installation 2-13 H9642 (Single-Bay) and H9645 (Wide-Body) Cabinets - Rear View 2-14 Installing Leveler Feet in the H9642 Cabinet 2-15 Stabilizer Arm Installation 2-16 Leveler Feet Adjustment 2-17 CPU Cabinet - Removing the RFI Shield Panel                                                                                                                                                                                                                                                                                                                                   | <i>L</i> -3          |

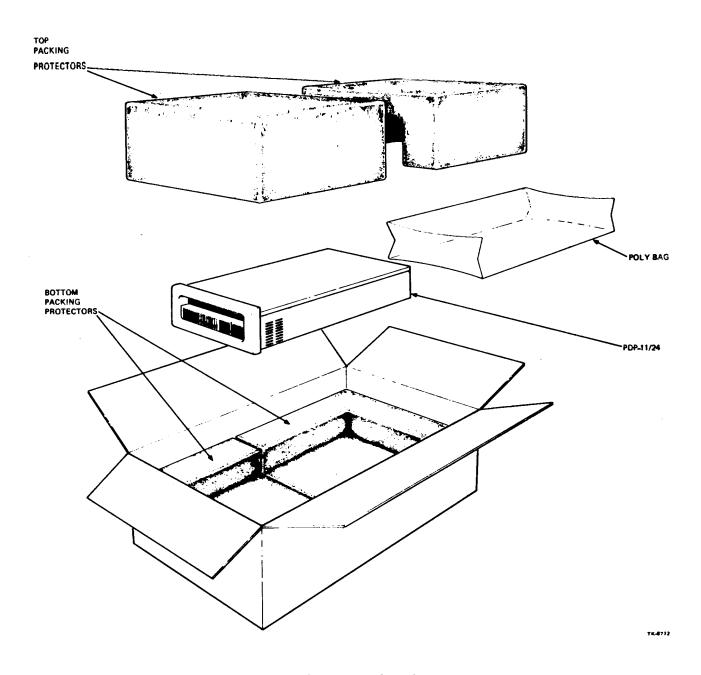

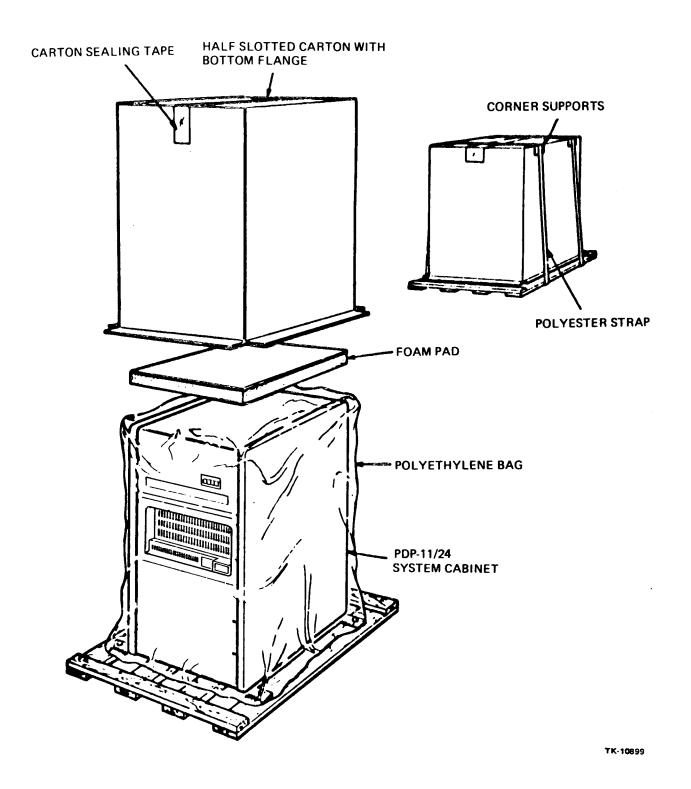

| PDP-11/24-AA, -AC, -BC Unit Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Z- <del></del>       |

| 2-4 Unpacking a PDP-11/24 System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Z-J                  |

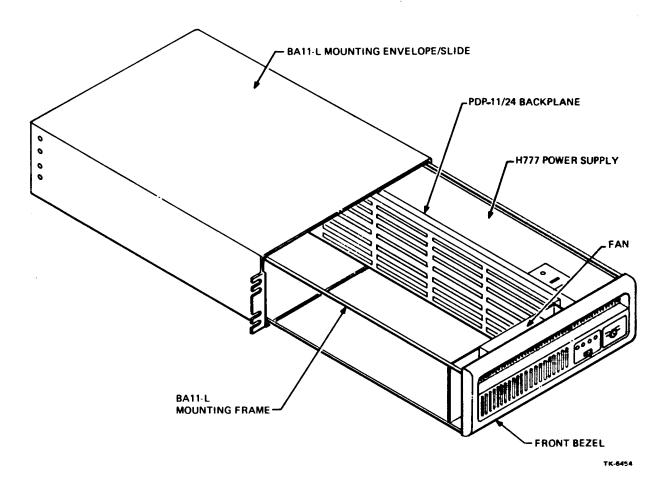

| 2-5 2-6 Mounting Envelope Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 270                  |

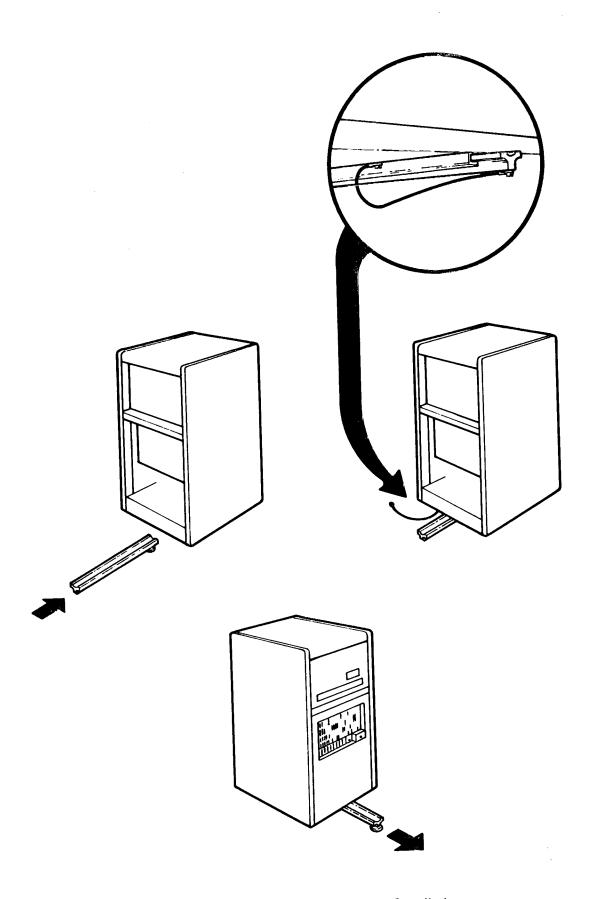

| Mounting Envelope Installation  2-7 PDP-11/24 System - CPU Mounting Box Fully Extended  2-8 BA11-AA, -AB Mounting Box Index Plate Installation  2-9 Single-Channel Slide Assembly  2-10 Designated Mounting Holes for Slide-Mounted PDP-11/24 CPUs Installed in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets  2-11 Cabinet Slide Installation  2-12 Mounting Box-to-Slide Installation  4 H9642 (Single-Bay) and H9645 (Wide-Body) Cabinets - Rear View  2-14 Installing Leveler Feet in the H9642 Cabinet  2-15 Stabilizer Arm Installation  2-16 Leveler Feet Adjustment  2-17 CPU Cabinet - Removing the RFI Shield Panel  Province K-reskeyt Panels in the RFI Shield Panel                                                                                                                                                                                                                                                                                                                                                                                                                      | <i>L- 1</i>          |

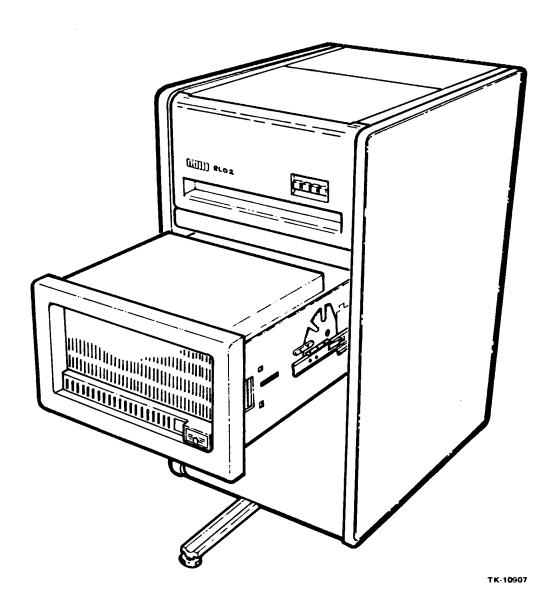

| 2-7 2-8 BA11-AA, -AB Mounting Box Index Plate Installation 2-9 Single-Channel Slide Assembly 2-10 Designated Mounting Holes for Slide-Mounted PDP-11/24 CPUs Installed in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets  2-11 Cabinet Slide Installation 2-12 Mounting Box-to-Slide Installation 2-13 H9642 (Single-Bay) and H9645 (Wide-Body) Cabinets - Rear View 2-14 Installing Leveler Feet in the H9642 Cabinet 2-15 Stabilizer Arm Installation 2-16 Leveler Feet Adjustment 2-17 CPU Cabinet - Removing the RFI Shield Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | , Z-O                |

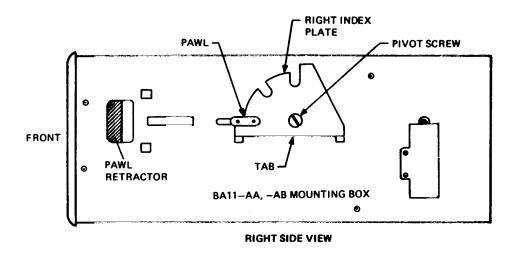

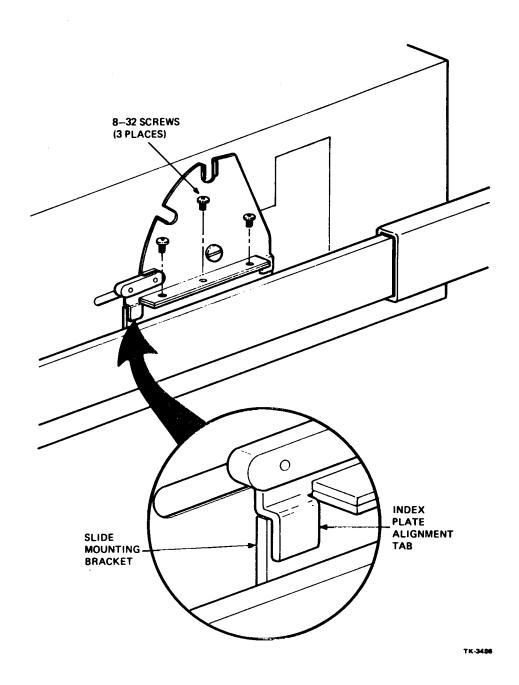

| 2-8 2-9 Single-Channel Slide Assembly Designated Mounting Holes for Slide-Mounted PDP-11/24 CPUs Installed in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets  2-11 Cabinet Slide Installation  2-12 Mounting Box-to-Slide Installation H9642 (Single-Bay) and H9645 (Wide-Body) Cabinets - Rear View 1-14 Installing Leveler Feet in the H9642 Cabinet 1-15 Stabilizer Arm Installation 2-16 Leveler Feet Adjustment 2-17 CPU Cabinet - Removing the RFI Shield Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | , <i>L</i> -7        |

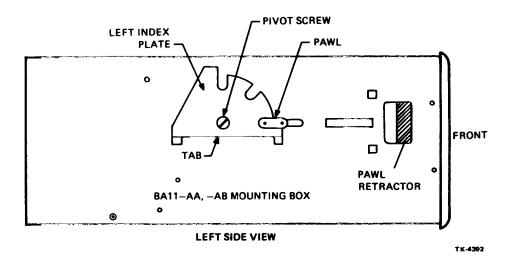

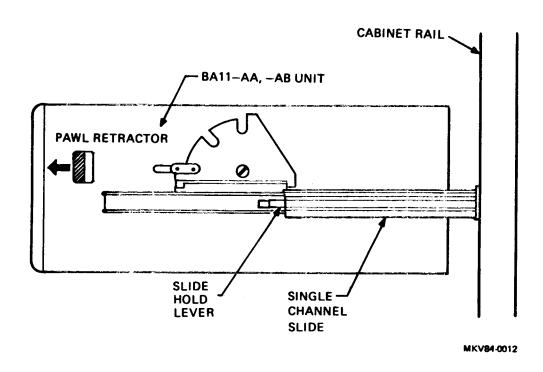

| 2-9 Single-Channel Slide Assembly Designated Mounting Holes for Slide-Mounted PDP-11/24 CPUs Installed in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets  2-11 Cabinet Slide Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-10                 |

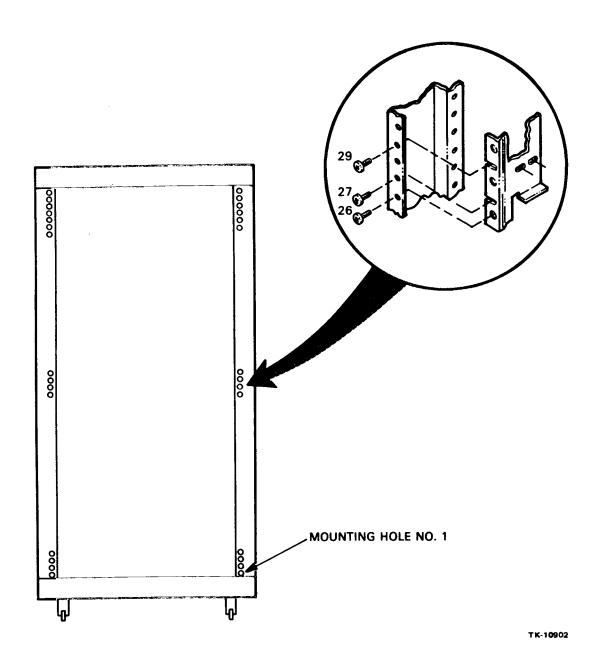

| 2-10 Designated Mounting Holes for Slide-Mounted PDP-11/24 CPUs Installed in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-11                 |

| in H9642 (Single-Bay) or H9645 (Wide-Body) Cabinets  2-11 Cabinet Slide Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

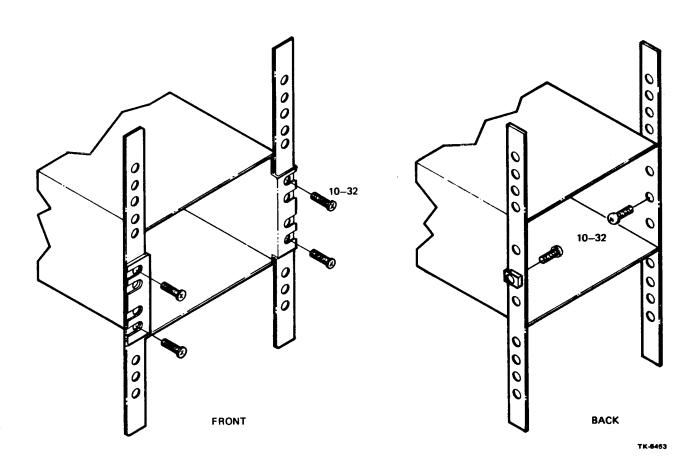

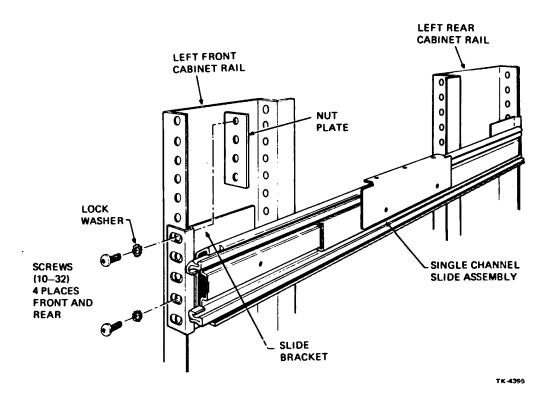

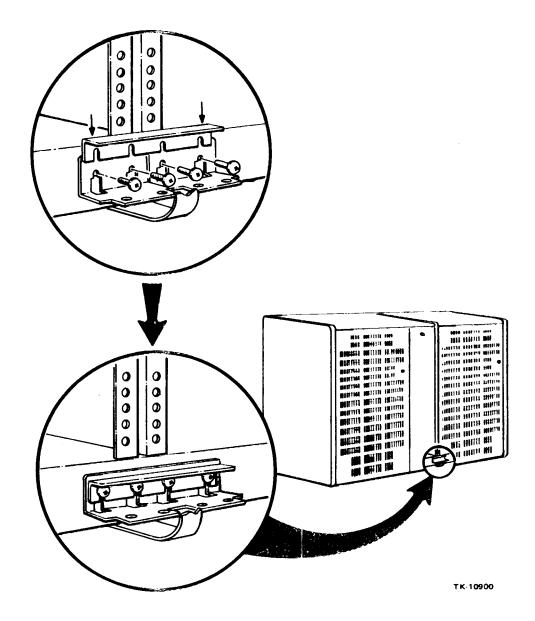

| 2-11 Cabinet Slide Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-12                 |

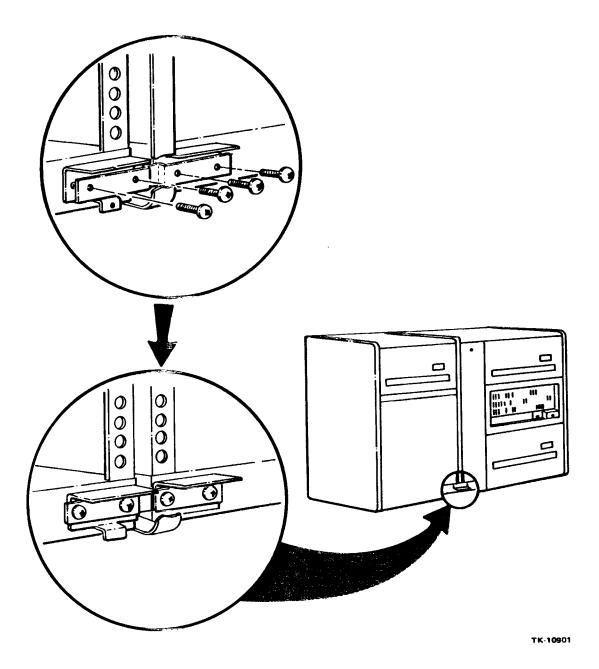

| 2-12 Mounting Box-to-Slide Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-13                 |

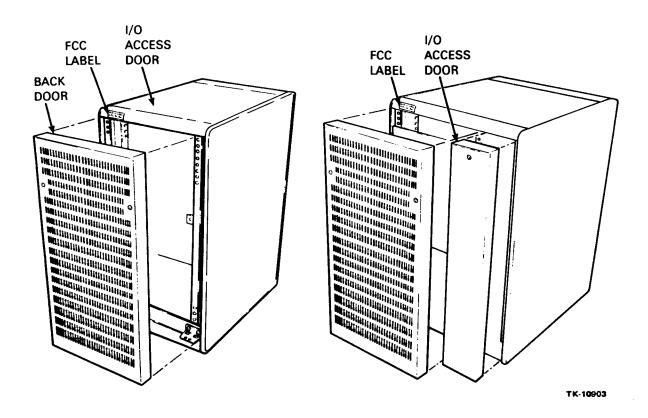

| 2-13 H9642 (Single-Bay) and H9645 (Wide-Body) Cabinets - Rear View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-17                 |

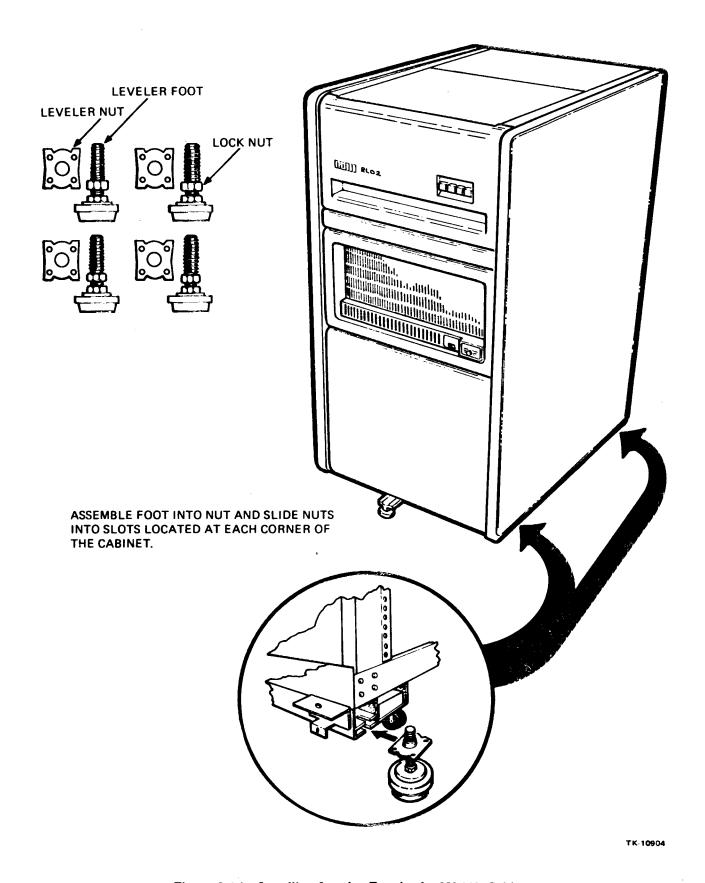

| 2-14 Installing Leveler Feet in the H9642 Cabinet  2-15 Stabilizer Arm Installation  2-16 Leveler Feet Adjustment  2-17 CPU Cabinet - Removing the RFI Shield Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Z-10                 |

| 2-15 Stabilizer Arm Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Z-1 /                |

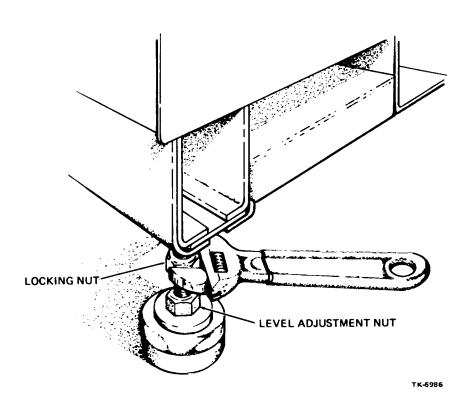

| 2-16 Leveler Feet Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <u>2</u> -10         |

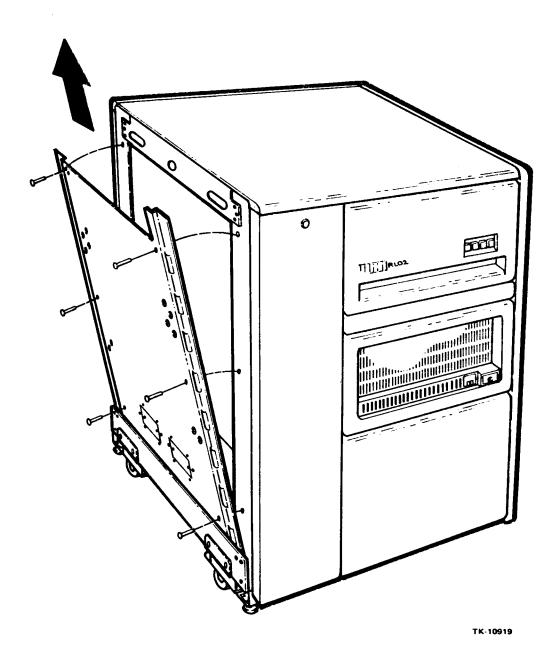

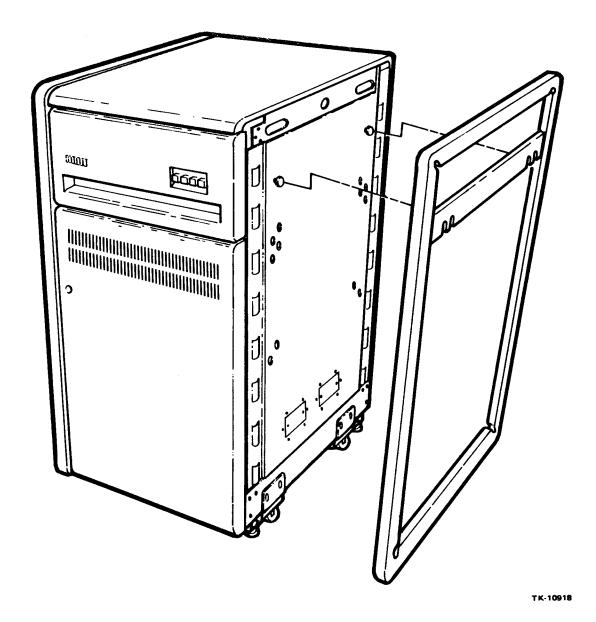

| 2-17 CPU Cabinet – Removing the RFI Shield Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4 <sup>-</sup> 17    |

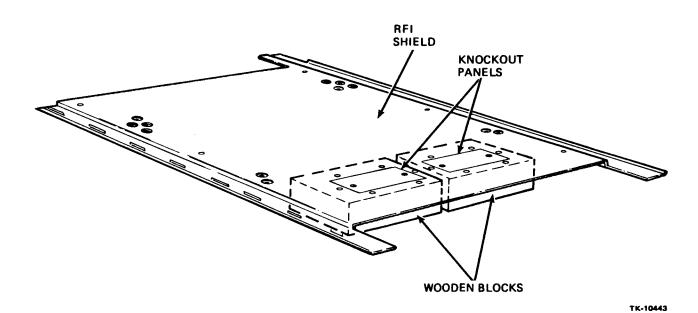

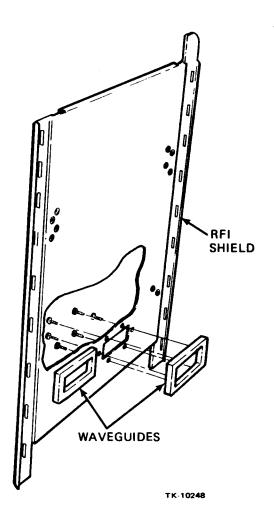

| Demander Vesskout Panels in the KEI Shield Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-21                 |

| 1-1 VEHIDANIS IZINOVORE I CHION III - FILA - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <i>L-LL</i>          |

| and Installation of Cable Port Flanges in the KFI Shield Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-23                 |

| 2 20 Paraying the Expander Panel from the H9642 Expander Cabinet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-4 <del>-</del>     |

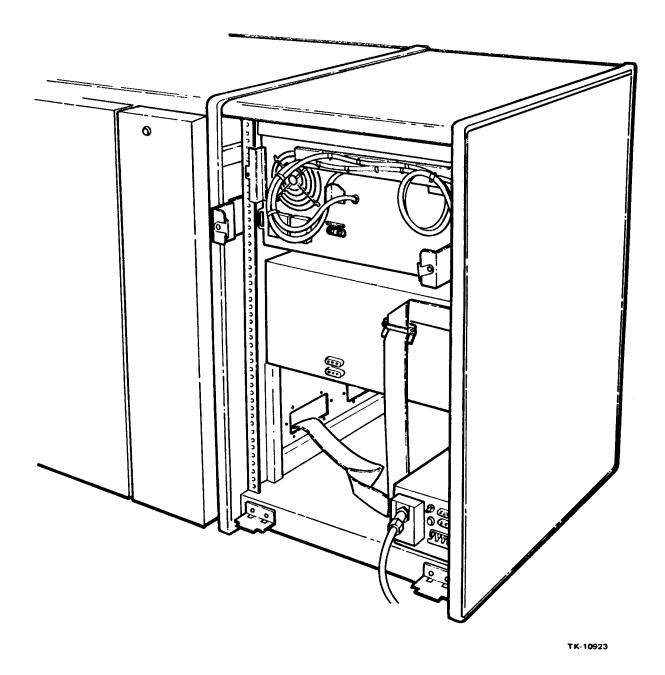

| a at Interior of LIO642 Expansion Cabinet - Kear View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Z-ZU                 |

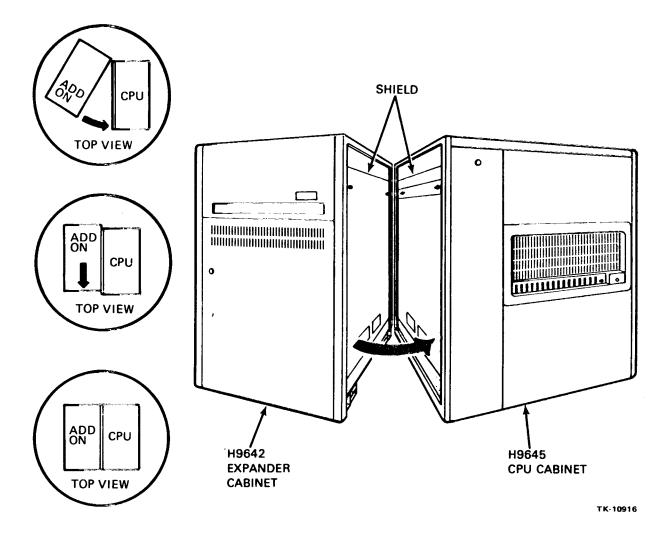

| 2 22 Joining the H9645 CPU Cabinet and the H9642 Expander Cabinet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-27                 |

| Detail of Front Interconnecting Ray Used in Joining the Hy040 CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| Cabinet and the H9642 Expander Cabinet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-28                 |

| Detail of Book Interconnecting Ray Used in Joining the H9043 CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

| Cabinet and the H9642 Expander Cabinet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-29                 |

| 2.25 DDD 11/24 Module Litilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-30                 |

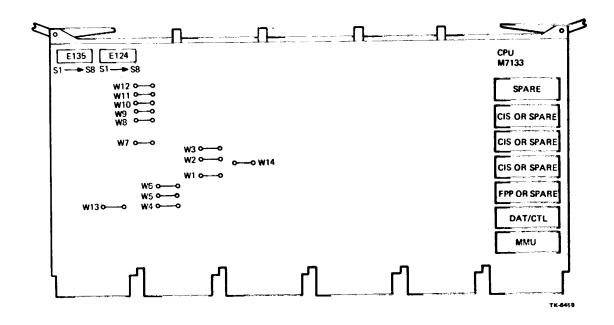

| DDD 11/24 CDI Module Jumper and Switch Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Z-J I                |

| A A A A A A A A A A A A A A A A A A A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Z-33                 |

| 2 20 LINIDIS Man Module Jumper Switch and KUM LOCATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Z-4U                 |

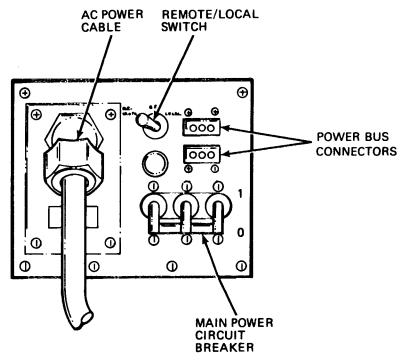

| 2 20 977 Power Controller - Front View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Z-40                 |

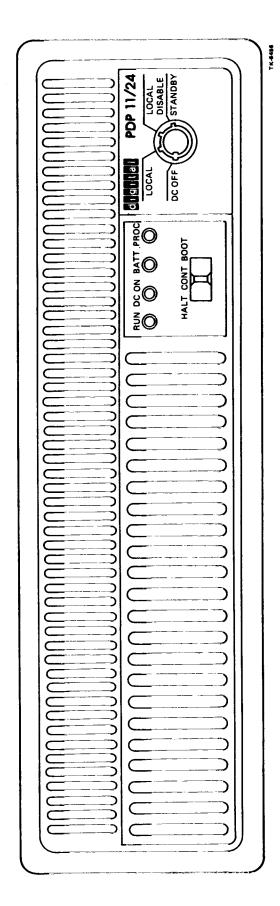

| DDD 11/24 Operator's Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-4                  |

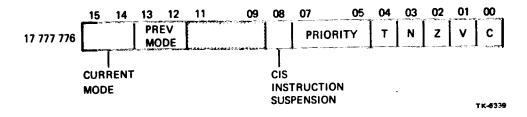

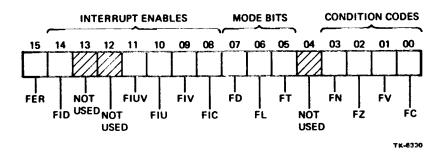

| 2.2 Decessor Status Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-13                 |

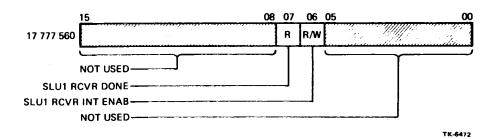

| 2.2 SLIII DCSD Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-14                 |

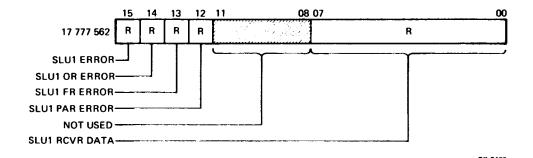

| 2.4 CI II DRIF Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-14                 |

| 2.5 CI III VCCD Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>3-</b> 1 <i>3</i> |

| 2.6 SULL VRUE Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-10                 |

| 2.7 CI I I DCCD Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <i>3</i> -1 /        |